TPG0224C General Business Use

Security Target-Lite

AT90SC28880RCFV2

# Table of Contents

| 1   | Introduction                                                                                        | .4 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 1.1 | Security Target Reference                                                                           | .4 |

| 1.2 | Purpose                                                                                             | .4 |

| 1.3 | References                                                                                          | .4 |

| 1.4 | TOE Overview                                                                                        | .5 |

|     | 1.4.1 TOE Reference                                                                                 | .5 |

|     | 1.4.2 TOE Definition                                                                                | .6 |

|     | 1.4.3 TOE life cycle                                                                                | 16 |

| 2   | Conformance Claims                                                                                  | 22 |

| 2.1 | CC Conformance Claim                                                                                | 22 |

| 2.2 | Package Claim                                                                                       | 22 |

| 2.3 | PP Claim                                                                                            | 22 |

| 2.4 | PP Refinements                                                                                      | 22 |

| 2.5 | PP Additions                                                                                        | 22 |

| 2.6 | PP Claims Rationale                                                                                 | 23 |

| 3   | Security Problem Definition                                                                         | 24 |

| 3.1 | Description of Assets                                                                               | 24 |

| 3.2 | Threats                                                                                             | 25 |

| 3.3 | Organisational Security Policies                                                                    | 26 |

| 3.4 | Assumptions                                                                                         | 27 |

| 4   | Security Objectives                                                                                 | 30 |

| 4.1 | Security Objectives for the TOE                                                                     | 30 |

| 4.2 | Security Objectives for the Security IC Embedded Software development Environment (not part of TOE) | 32 |

| 4.3 | Security Objectives for the operational Environment                                                 | 34 |

| 4.4 | Security Objectives Rationale                                                                       | 35 |

| 5   | Extended Components Definition                                                                      | 36 |

| 6   | IT Security Requirements                                                                            | 37 |

| 6.1 | Security Functional Requirements for the TOE                                                        | 38 |

| 6.2 | Security Assurance Requirements for the TOE                                                         | 51 |

|     | 6.2.1 Refinements of the TOE Assurance Requirements                                                 | 52 |

| 6.3 | Security Requirements Rationale                                                                     | 52 |

|     | 6.3.1 Rationale for the security functional requirements                                            | 52 |

TPG0224C-VIC-09Dec13

|     | 6.3.2 Dependencies of security functional requirements | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TOE Summary Specification                              | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.1 | Description of TSF Features of the TOE                 | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

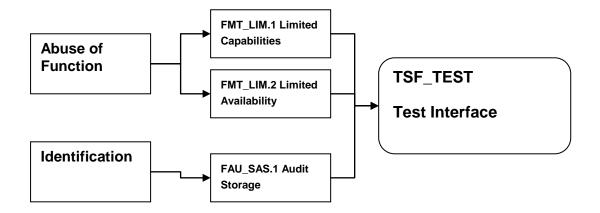

|     | 7.1.1 TSF_TEST Test Interface                          | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

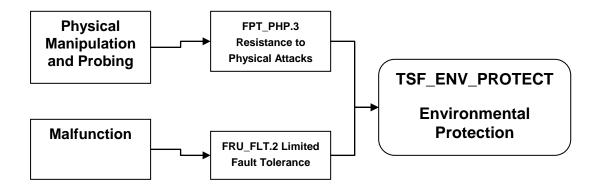

|     | 7.1.2 TSF_ENV_PROTECT Environmental Protection         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

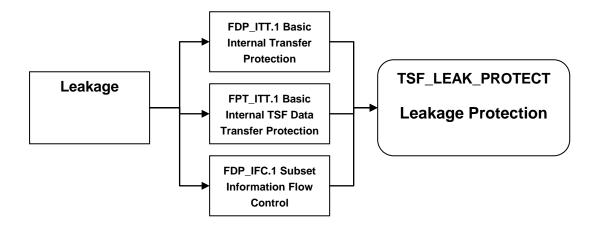

|     | 7.1.3 TSF_LEAK_PROTECT Leakage Protection              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

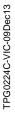

|     | 7.1.4 TSF_DATA_PROTECT Data Protection                 | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

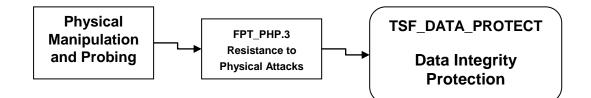

|     | 7.1.5 TSF_AUDIT_ACTION Event Audit and Action          | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

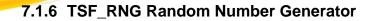

|     | 7.1.6 TSF_RNG Random Number Generator                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

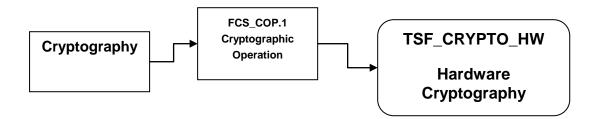

|     | 7.1.7 TSF_CRYPTO_HW Hardware Cryptography              | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

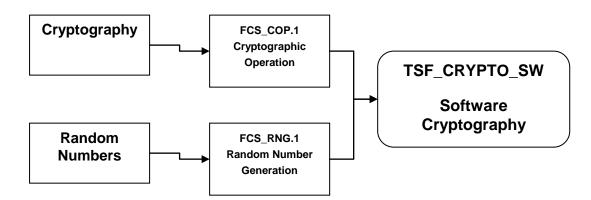

|     | 7.1.8 TSF_CRYPTO_SW Toolbox Cryptography               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.2 | Rationale for TSF                                      | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 7.2.1 Summary of TSF to SFR                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 7.2.2 Note on ADV_ARC.1                                | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8   | Annex                                                  | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.1 | Glossary of Vocabulary                                 | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.2 | Literature                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.3 | List of Abbreviations                                  | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 7.1<br>7.2<br><b>8</b><br>8.1<br>8.2                   | <ul> <li>7 TOE Summary Specification</li> <li>7.1 Description of TSF Features of the TOE</li> <li>7.1.1 TSF_TEST Test Interface</li> <li>7.1.2 TSF_ENV_PROTECT Environmental Protection</li> <li>7.1.3 TSF_LEAK_PROTECT Leakage Protection</li> <li>7.1.4 TSF_DATA_PROTECT Data Protection</li> <li>7.1.5 TSF_AUDIT_ACTION Event Audit and Action</li> <li>7.1.6 TSF_RNG Random Number Generator</li> <li>7.1.7 TSF_CRYPTO_HW Hardware Cryptography</li> <li>7.1.8 TSF_CRYPTO_SW Toolbox Cryptography</li> <li>7.2 Rationale for TSF.</li> <li>7.2.1 Summary of TSF to SFR</li> <li>7.2.2 Note on ADV_ARC.1</li> <li>8 Annex</li> <li>8.1 Glossary of Vocabulary</li> </ul> |

# 1 Introduction

# 1.1 Security Target Reference

Title:AT90SC28880RCFV2 Security TargetVersion number:CSponsor:INSIDE SECUREEvaluation Scheme:France (ANSSI)Evaluator:LETI

| Version | Date      | Changes                                                                                                  | Author        |

|---------|-----------|----------------------------------------------------------------------------------------------------------|---------------|

| A       | 03 Jun 13 | First release                                                                                            | John Boggie   |

| В       | 03 Oct 13 | TOE references changed from B to C. SN_1 identifier updated.<br>Guidance list updated to latest version. | Graeme Calder |

| С       | 09 Dec 13 | Updated guidance list to latest versions.                                                                | Graeme Calder |

#### 1.2 Purpose

1 This document defines the Security Target of the AT90SC28880RCFV2 project, and is provided to satisfy the Assurance Class ASE Security Target Evaluation as defined in Part 3 [CC\_PART3] of the Common Criteria version 3.1, Revision 4.

#### 1.3 References

2 The table below lists only the documents that are referenced in this Security Target to give the user further information. Section 1.4 the TOE overview lists the User Guidance documents applicable to the Security IC Embedded Software Developer. Section 8.2 lists the Standards used to perform the certification of the TOE.

| [TDS]     | Semi-Formal TOE Design               |

|-----------|--------------------------------------|

| [FSP]     | Semi-Formal Functional Specification |

| [DESSPEC] | Design Specifications                |

| [ARC]     | Security Architecture Description    |

| [COF]     | Customer Option Form                 |

Note: For the correct version of the above documents, the user of this document should refer to the TOE Deliverables list (EDL).

# 1.4 TOE Overview

## 1.4.1 TOE Reference

3 The Target of Evaluation is a Secure Microcontroller with Cryptographic Software library. The TOE is identified as shown below:

|                               |                                 | Identifier (FAU_SAS.1 where applicable) |

|-------------------------------|---------------------------------|-----------------------------------------|

| Part Number                   | AT90SC28880RCFV2                | SN_0 = 0x61 [TD]                        |

| Product Identification Number | 59U21                           |                                         |

| Hardware Revision             | <mark>C</mark> (LFoundry)       | SN_1 = 0x0 <mark>2</mark> [GEN_TD]      |

|                               | C (UMC)                         | SN_1 = 0x8 <mark>2</mark> [GEN_TD]      |

| Applicable Inside Toolbox(s)  | 00.03.2x.xx Family <sup>a</sup> |                                         |

|                               | 00.03.22.04                     | 0x00032204 <sup>b</sup>                 |

|                               | 00.03.21.03                     | 0x00032103                              |

|                               | 00.03.20.02                     | 0x00032002                              |

|                               | 00.03.24.02                     | 0x00032402                              |

- 4 The TOE is a dual interface Secure Microcontroller (Security IC) that may be used in a variety of security applications, including, Banking, Identification, Pay TV and embedded systems.

- 5 The increase in the number and complexity of applications in the market of a Secure Microcontroller is reflected in the increase of the level of data security required. The security needs for the TOE can be summarised as being able to counter those who want to defraud, gain unauthorised access to data and control a system utilising the TOE. Therefore it is mandatory to:

- maintain the integrity and the confidentiality of the content of the TOE memories as required by the end application(s)

The toolbox identification is output by the TOE when the self test function of the toolbox is called

TPG0224C-VIC-09Dec13

<sup>&</sup>lt;sup>a</sup> The Customer has the option to choose any member of the 00.03.2x.xx family of toolboxes, each toolbox is a subset of the 00.03.22.xx toolbox. This ST clearly states the functions applicable to each toolbox. Further information is given in section 1.4.2.2

- maintain the correct execution of the software residing on the TOE

- 6 This requires that the TOE especially maintains the integrity and the confidentiality of its security functionality.

- 7 Protected information is in general secret or integrity sensitive data such as Personal Identification Numbers, Balance Value (Stored Value Cards), and Personal Data Files. Other protected information data representing the access rights; these include any cryptographic algorithms and keys needed for accessing and using the services provided by the system through use of the Security IC.

- 8 The TOE can be used in a smartcard application, a USB token or other devices. The intended environment is very large; and generally once issued the TOE may be stored and used anywhere, generally there is no control applied to the TOE and its operational environment.

- 9 The TOE is a Dual interface chip that can be operated in either Contact or Contactless communication mode.

#### 1.4.2 TOE Definition

#### 1.4.2.1 TOE Overview

#### **General Features**

- High-performance, Low-power secure 8-/16-bit Enhanced RISC Architecture

- 135 Powerful Instructions (Most Executed in a Single Clock Cycle)

- Low-power Idle and Power-Down Modes

- Bond Pad Locations Conforming to ISO 7816-2

- ESD Protection to  $\pm$  5kV on ISO and  $\pm$  4kV RF pins

- Operating Ranges: from 2.7V to 5.5V

- Compliant with EMV 4.3 Specifications and CQM

- Compliant with ICAO e-Passport Specifications

- Available in Wafers, Modules, Contactless Modules, Inlays and Industry-standard Packages

- Compatible with Printed Antennas (losses from 10 to 20 Ohms)

#### Memory

- 256K bytes ROM Program Memory and 32K bytes of ROM with specific access.

- 80K bytes EEPROM, Including 128 OTP Bytes and 384 Bit-addressable Bytes

- 1 to 64-byte Program/Erase

- 1ms Program, 1ms Erase

6 of 72

- Endurance: 500,000 Write/Erase Cycles at 25°C

- 22 Years Data Retention

- 8K bytes RAM Memory (6K bytes of CPU RAM, 2K bytes of Ad-X<sup>™</sup>2 RAM, shared with the 8-/16-bit RISC CPU) + 256 Bytes of DMA dedicated RAM

- 32K Bytes of ROM dedicated to Inside's Crypto Library

#### Peripherals

- One I/O Port

- One ISO 7816 Controller

- Up to 625 kbps at 5 MHz

- Compliant with T = 0 and T = 1 Protocols

- Programmable Internal Oscillator (Up to 30 MHz for Ad-X2 and internal CPU Clock)

- Three 16-bit Timers (One in contact, One in contactless, One shared for contact/contactless)

- Random Number Generator (RNG)

- 2-level Interrupt Controller

- Hardware DES and Triple DES DPA/DEMA Resistant (Four keys)

- Hardware AES

- Code Signature Module

- CRC16 & 32 Engine (Compliant with ISO/IEC 3309)

- 32-Bit Cryptographic Accelerator (Ad-X2 for Public Key Operations) :

- RSA, DSA, ECC, Diffie-Hellman

#### Contactless

- Contactless Interface Controller (CIC) with Full Support for ISO/IEC 14443 Type B

Protocol

- Compliant with ISO 14443 and ISO 10373-6 Specifications

- Supply Voltage Clamp and Regulation

- On-chip Tuning Capacitance: 92pF

- Baud Rates: 106Kbps, 212Kbps, 424Kbps and 848Kbps

- Very High Bit Rates (VHBR): 1.7Mbps, 3.4Mbps and 6.8Mbps for Card to Reader communication

- DMA capability

AT90SC28880RCFV2

- Dedicated Hardware for Protection Against SPA/DPA/SEMA/DEMA Attacks

- Advanced Protection Against Physical Attack, Including Active Shield, EPO, CStack Checker, Slope Detector, Parity Errors.

- Environmental Protection Systems

- Voltage Monitor

- Frequency Monitor

- Temperature Monitor

- Light Protection

- Glitch Protection

- Secure Memory Management/Access Protection (Supervisor Mode)

- Start on Internal Oscillator

- No External Clock for Contactless Mode

# Security IC Embedded Software Developer Guidance Documents

| REF                | Title                                                            | Inside<br>Identifier | Version | Note                                                                                                                 |

|--------------------|------------------------------------------------------------------|----------------------|---------|----------------------------------------------------------------------------------------------------------------------|

| [WSR]              | Wafer saw Recommendations                                        | TPG0079              | В       | Wafer saw Guidelines                                                                                                 |

| [ACT]              | SmartACT User's Manual                                           | TPR0134              | D       | Security IC developer Code<br>entry user manual                                                                      |

| [APP_DES]          | Secure Hardware DES/TDES on<br>AT90SC 0.13µm products            | TPR0400              | L       | Hardware TDES<br>recommendations                                                                                     |

| [APP_CSM]          | The Code Signature Module for 0.13µm products                    | TPR0409              | С       | Datasheet for the Code<br>Signature Module                                                                           |

| [APP_AES]          | Secure Hardware AES on AT90SC products (.13µm)                   | TPR0428              | E       | Hardware AES recommendations                                                                                         |

| [GEN-TD]           | AT90SC 0.13 µm products                                          | TPR0447              | E       | Hardware Datasheet details the FSP                                                                                   |

| [APP_AD-<br>X2]    | Ad-X2 Datasheet                                                  | TPR0452              | D       | Ad-X2 Hardware Datasheet                                                                                             |

| [APP_SEC]          | Security Recommendations for 0.13µm products - 2                 | TPR0456              | E       | General Security recommendations for the TOE                                                                         |

| [APP_CUST<br>_TBX] | Efficient use of Ad-X2                                           | TPR0463              | С       | Guidance for customers who<br>wish to use their own<br>Cryptographic Toolbox                                         |

| [APP_RNG]          | Generating Random numbers to known standards for 0.13µm products | TPR0468              | E       | Details how to write an AIS31<br>driver using the hardware and<br>the AIS31 test routines from<br>the Inside toolbox |

| [APP_TBX]          | Toolbox 00.03.2x.xx on AT90SCxxxxC                               | TPR0504              | E       | Toolbox 00.03.2x.xx<br>Datasheet details the FSP for<br>the Toolbox functions                                        |

| [APP_TBX_<br>SEC]  | Secure use of Tbx 00.03.2x.xx on AT90SC                          | TPR0505              | F       | Toolbox 00.03.2x.xx family Security recommendations                                                                  |

| [TD]               | AT90SC28880RCFV2 Technical<br>Datasheet                          | TPR0548              | D       | Hardware Datasheet details the FSP                                                                                   |

TPG0224C-VIC-09Dec13

# AT90SC28880RCFV2

# TOE Life Cycle Addresses

| Function              | Company        | Location                                                                |

|-----------------------|----------------|-------------------------------------------------------------------------|

| IC Design             | Inside Secure  | Inside Secure                                                           |

| Dataprep              | (RFO)          | Vault-IC Division                                                       |

| Cryptographic Support |                | Zone Industrielle Peynier Rousset                                       |

| Software Development  |                | 13106 Rousset - FRANCE                                                  |

| IC Design             | Inisde Secure  | Inside Secure                                                           |

|                       | (AIX)          | Parc du Golf, 350 rue Guilibert Gauthier de la Lauzière, ZI Les Milles, |

|                       |                | 13856 Aix en Provence                                                   |

| IC Design             | Inside Secure  | Inside Secure                                                           |

|                       | (EKB)          | Vault-IC Division                                                       |

|                       |                | Scottish Enterprise Technology Park                                     |

|                       |                | East Kilbride - SCOTLAND                                                |

| IC Design             | Inside Secure  | Inside Secure                                                           |

|                       | (Nice)         | Space Antipolis 9                                                       |

|                       |                | 2323 chemin St-Bernard                                                  |

|                       |                | 06225 Vallauris Cedex                                                   |

| IC Design             | Inside Secure  | Inside Secure                                                           |

|                       | (Singapore)    | 77 science park drive #02-18/19                                         |

|                       |                | CINTECH III                                                             |

|                       |                | SINGAPORE 118256                                                        |

| IC Design             | Inside Secure  | INSIDE Secure POLAND Sp. z o.o.                                         |

|                       | (Warsaw)       | ul. Ostrobramska 101/336                                                |

|                       |                | 04-041 Warszawa                                                         |

|                       |                | POLAND                                                                  |

| Wafer Fab             | Lfoundry       | Lfoundry Rousset                                                        |

|                       |                | Zone Industrielle                                                       |

|                       |                | 13106 Rousset Cedex                                                     |

|                       |                | France                                                                  |

| Wafer Fab             | UMC            | Fab 8C, 8D No. 3, Li-Hsin 2nd Road,                                     |

|                       |                | Hsinchu Science Park,                                                   |

|                       |                | Hsin-Chu                                                                |

|                       |                | Taiwan                                                                  |

| Mask Shop             | Toppan Dresden | Toppan Photomasks Europe                                                |

|                       |                | Rahnitzer Allee 9                                                       |

|                       |                | 01109 DRESDEN - GERMANY                                                 |

| Mask Shop             | TCE            | 1127-3 Hopin Road                                                       |

TPG0224C-VIC-09Dec13

AT90SC28880RCFV2

| Function    | Company        | Location                                                                  |

|-------------|----------------|---------------------------------------------------------------------------|

|             |                | Padeh City                                                                |

|             |                | Taoyuan                                                                   |

|             |                | Taiwan 30080                                                              |

| Mask Shop   | Toppan Corbeil | Toppan Photomasks Europe                                                  |

|             |                | 224, boulevard John Kennedy                                               |

|             |                | 91105 CORBEIL-ESSONNES                                                    |

|             |                | FRANCE                                                                    |

| Mask Shop   | Compugraphics  | Compugraphics International Limited                                       |

|             |                | Newark Road North                                                         |

|             |                | Eastfield Industrial Estate                                               |

|             |                | KY7 4NT                                                                   |

|             |                | Scotland                                                                  |

| Test Centre | ASE            | Advanced Semiconductor Engineering                                        |

|             |                | 26 Chin 3 <sup>rd</sup> Rd                                                |

|             |                | Nantze Export Processing Zone                                             |

|             |                | Kaohsiung                                                                 |

|             |                | Taiwan                                                                    |

| Test Centre | UTAC           | Address: 73 Moo 5, Bangsamak, Bangpakon                                   |

|             |                | Chachoengsao 24180, THAILAND                                              |

| Test Centre | Chipbond       | CHIPBOND TECHNOLOGY CORPORATION                                           |

|             |                | KAOHSIUNG BRANCH NO.5, SOUTH 6TH<br>ROAD, K.E.P.Z. KAOHSIUNG, TAIWAN, R.C |

| Wafer Saw   | DISCO          | Kirchheim bei Munich - GERMANY                                            |

# 1.4.2.2 TOE Description

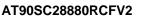

#### 10 Figure 1 gives an overview of the AT90SC28880RCFV2 device

Figure 1: Block Diagram of the AT90SC28880RCFV2 TOE

11 The Target of Evaluation (TOE) is Secure Microcontroller (Security IC) it is composed of a processing unit, security components, I/O port, ROM, EEPROM, and RAM memories.

- 12 The TOE will contain software elements during its life cycle. This software falls into 2 distinct categories:

- IC Dedicated Software comprising

- o IC Dedicated Test Software

- IC Dedicated Support Software (Cryptographic Support Software)

- Security IC Embedded Software

- IC Dedicated Test Software: Test Software includes the test programs that are 13 produced as evidence to support the ATE class for the evaluation of the TOE. INSIDE Engineering ROM is provided to facilitate testing of the device; this Engineering ROM is applicable to Phases 2 and 3 of the TOE life Cycle. To further aid testing of the TOE, additional test programs may be loaded into the EEPROM. In addition to the Test Software, the TOE also includes dedicated hardware to perform testing. To allow the ITSEF to perform testing of the TOE, the TOE is delivered with an INSIDE Engineering ROM (it should be noted this also includes the Cryptographic Support Software detailed below) and some simple test routines stored in the EEPROM. It must be noted that this Engineering ROM and associated Test Software is not part of the TOE (apart from the Cryptographic Support Software, which is part of the TOE). The entry and abuse of test modes (hardware) must be verified after TOE Delivery: this is evaluated according to the Common Criteria assurance family AVA\_VAN. Refer to TOE Summary Specification for further information.

- 14 Cryptographic Support Software (Toolbox): The TOE where applicable also consists of a Cryptographic Toolbox provided by INSIDE. This Toolbox is part of the ROM embedded on the TOE within the Secure Core. The user of this document should refer to the TOE Summary specification of this document for the full details. The INSIDE Toolbox is considered part of the TOE.

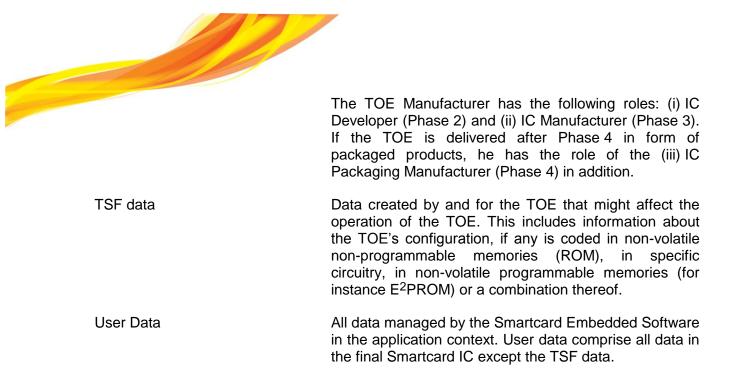

- 15 Security IC Embedded Software: The final version of the AT90SC28880RCFV2 device also includes embedded software; this final version of the product is referred to as a Composite Product. The Security IC Embedded Software can be stored in non-volatile non-programmable memories (ROM). However, some parts of it (called supplements for the Security IC Embedded Software, refer to [PP]) may also be stored in non-volatile programmable memories (for instance EEPROM). All data managed by the Security IC Embedded Software is called User Data. In addition, Pre-personalisation Data [PP] belongs to the User Data.

- 16 The Composite Product comprises

- the TOE

- the Security IC Embedded Software comprising

- Hard-coded Security IC Embedded Software (normally stored in ROM)

- Soft-coded Security IC Embedded Software (normally stored in EEPROM) and

- User Data (especially personalisation data and other data generated and used by the Security IC Embedded Software)

- 17 The Security IC Embedded Software and the User Data are developed separately to the hardware TOE by the Inside Customers. The Security IC Embedded Software is not part of the TOE.

**Note:** even though the Security IC Embedded Software is not part of the TOE, the documentation delivered as evidence for the AGD Class (**Guidance Documentation**) aid the developer to ensure the correct operation of the device and more importantly the security functionality of the device. **Therefore, the Guidance Documentation is considered part of the TOE**.

- 18 Therefore, the TOE comprises

- the circuitry of the IC (hardware including the physical memories)

- initialisation data related to the IC Dedicated Software and the behaviour of the security functionality <sup>a</sup>

- the associated guidance documentation

- Cryptographic Support Software

The TOE is designed, and generated by the TOE Manufacturer

- 19 The TOE is intended to be used for a Secure Microcontroller product (Security IC), independent of the physical interface and the way it is packaged. Generally, a Security IC product may include other optional elements (such as specific hardware components, batteries, capacitors, antennae) but these are not in the scope of this Security Target.

- 20 Note that the Security IC is usually packaged. However, the way it is packaged is not specified here.

<sup>&</sup>lt;sup>a</sup> which may also be coded in specific circuitry of the IC; for a definition refer to the Glossary.

General Business Use

AT90SC28880RCFV2

# 1.4.2.3 Cryptographic Toolbox Software

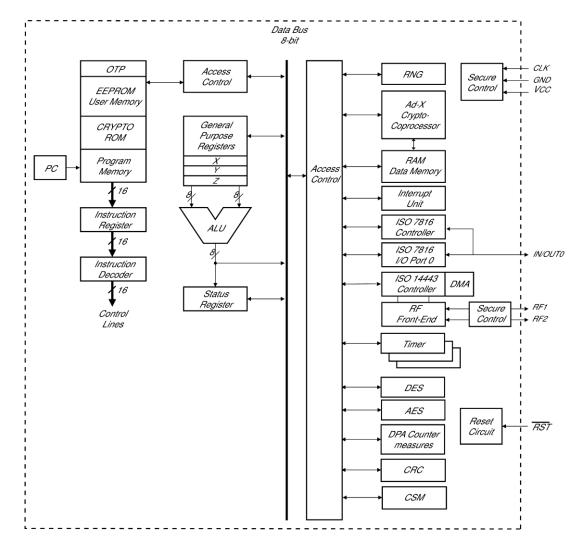

22 The TOE contains a member of the 00.03.2x.xx Inside Toolbox family. The 00.03.2x.xx family consists of 4 variants. The 4 variants are related to each other as shown.

Figure 2: Cryptographic Toolbox Software

23 Toolbox 00.03.22.xx contains the full set of cryptographic functions; 00.03.21.xx is a subset of 00.03.22.xx. 00.03.20.xx is a subset 00.03.21.xx. 00.03.24.xx is a subset of 00.03.20.xx. Therefore, all the functions available in the 00.03.24.xx are available in 00.03.20.xx, 00.03.21.xx and 00.03.22.xx and so on.

# 1.4.3 TOE life cycle

24 This Security Target is fully conformant to the claimed PP, the full details of the Security IC life cycle is shown in the PP. This Security Target gives a short summary of the information given in the PP. Information is also given within this Security Target to expand on the applicable phases of the life cycle of the TOE.

# **1.4.3.1 Overview of the Composite Product Life Cycle**

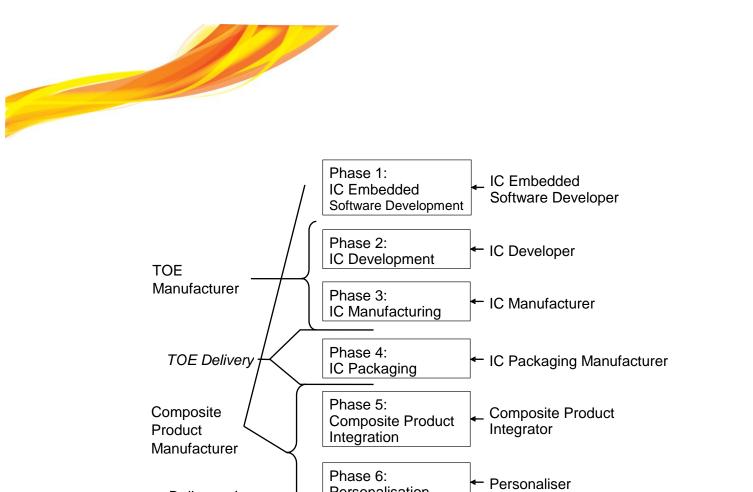

- 25 The complex development and manufacturing processes of a Composite Product can be separated into seven distinct phases. The phases 2 and 3 of the Composite Product life cycle cover the TOE (IC) development and production:

- The IC Development (Phase 2):

- IC design

- IC Dedicated Software development

- The IC Manufacturing (Phase 3):

- integration and photomask fabrication

- IC production

- IC testing

- preparation

- Pre-personalisation if necessary

- 26 In addition, five important stages have to be considered in the Composite Product life cycle:

- Security IC Embedded Software Development (Phase 1) (not part of the TOE)

- the IC Packaging (Phase 4)

- the Composite Product finishing process, preparation and shipping to the personalisation line for the Composite Product (Composite Product Integration Phase 5)

- the Composite Product personalisation and testing stage where the User Data is loaded into the Security IC's memory (Personalisation Phase 6)

- the Composite Product usage by its issuers and consumers (Operational Usage Phase 7) which may include loading and other management of applications in the field

Delivery of Composite Product

Personalisation

Personaliser

Product

Phase 7: Operational Usage

Consumer of Composite Product (End-Consumer)

Figure 2: Definition of "TOE Delivery" and responsible Parties

- 27 The Security IC Embedded Software is developed outside the TOE development in Phase 1. The TOE is developed in Phase 2 and produced in Phase 3. Then the TOE can be delivered in the form of wafers or sawn wafers (dice).

- 28 In the following the term "TOE Delivery" (refer to Figure 2) is uniquely used to indicate

- after Phase 3 (or before Phase 4) if the TOE is delivered in the form of wafers or sawn wafers (dice).

- The Security Target uniquely uses the term "TOE Manufacturer" (refer to Figure 2) which includes the following roles:

- the IC Developer (Phase 2) and the IC Manufacturer (Phase 3)

The TOE is delivered after Phase 3 in the form of wafers or sawn wafers (dice).

29 Hence, the "TOE Manufacturer" comprises all roles beginning with Phase 2 and before "TOE Delivery". Starting with "TOE Delivery", another party takes over the control of the TOE.

- 30 The Security Target uniquely uses the term "Composite Product Manufacturer" which includes all roles (outside TOE development and manufacturing) except the Endconsumer as user of the Composite Product (refer to Figure 2) which are the following:

- Security IC Embedded Software development (Phase 1)

- the IC Packaging Manufacturer (Phase 4) if the TOE is delivered after Phase 3 in the form of wafers or sawn wafers (dice)

- the Composite Product Manufacturer (Phase 5) and the Personaliser (Phase 6).

#### 1.4.3.2 Phases 2 and 3 of the TOE Life Cycle

#### 1.4.3.3 Phase 2 IC Development

- 31 The development of the TOE is applicable to phase 2 of the life cycle and can be split into two sections:

- IC design

- Cryptographic Support Software Development

- 32 **IC design:** IC design takes place across two locations, the Inside Design Centre in East Kilbride Scotland (EKB), and the design centre in Rousset France (RFO). The main project design team is located in EKB but some modules or libraries may originate in other Inside Secure design locations.

- 33 **Cryptographic Support Software Development:** The Toolbox development takes place within the Inside Design Centre in France.

- 34 To ensure security of the design centres, IC design takes place within a secure environment; access is controlled with full traceability. A dedicated security person is on site at all times. The IC and Toolbox development is achieved using appropriate development tools running on a secure network. All access to tools and data are controlled using appropriate restrictions and passwords. The full details are shown within the evidence provided for the ALC class. On completion of the design database, the data is transferred from Design to Dataprep to allow for generation of the Photomasks used to manufacture the TOE.

Phase 3 IC Manufacturing

- 35 The IC manufacturing falls into three sections

- Dataprep and Mask Shop

- Wafer Fab

- Testing

- 36 **Dataprep and Mask Shop:** The design database is delivered from the design centre to the Dataprep team within Inside. This delivery and acceptance process and associated outputs are delivered as part of the evidence provided for the ALC class. The Photomasks used to manufacture the TOE are created by the Mask Shop. Data is transferred from Inside Secure to the Mask Shop by secure FTP. Once created the Photomasks are transferred to the Wafer Fab by a secure approved carrier. This transfer includes tamper evidence and full traceability.

- 37 **Wafer Fab:** The TOE is manufactured within a Wafer Fabrication facility. The fabrication process occurs within the secure facility, as with the protection mechanisms in place in Phase 2 access to the fabrication facility is restricted. The batches are controlled using a tracking database to ensure that there is traceability of wafers at all times (including rejected wafers/dies). On completion of the fabrication process, the wafers are transferred to the test facility for test and pre-personalisation. Transfer is by a secure carrier, includes tamper evidence, and has full traceability.

- **Testing:** This stage of the process includes production testing (refer to ATE evidence), pre-personalisation, configuration of the security functionality, wafer thinning and saw. The test facility has a controlled environment, access is restricted with full traceability, and dedicated security personnel are on site at all times.

# 1.4.3.4 Modes of Operation and Life Cycle Phases

39 The TOE has three distinct modes of operation

| Test Mode    | This mode is designed to allow <b>authenticated test</b><br><b>engineers</b> access to Test features of the TOE. This mode<br>of operation is applicable up to the end of Phase 3 of the<br>life cycle. This mode of operation is disabled by wafer<br>saw. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Mode | This mode is designed to allow <b>authenticated test</b><br><b>engineers</b> access to a <b>subset</b> of the Test features of the<br>TOE. This mode of operation is applicable to the full life<br>cycle of the TOE.                                       |

| User Mode    | This is the Mode of operation that the end Security IC (composite product) is intended to be used in. This mode of operation is dependent on the ROM and NVM code loaded. This mode of operation is available throughout the life cycle of the TOE.         |

# 1.4.3.5 Composite Product Manufacturer Phases of the Life Cycle

- 40 Although the pertinent phases of the Life Cycle associated with the TOE and this Security Target are Phases 2 and 3, it should be noted that parts of the TOE and this Security Target relate to Phase 1 of the TOE life Cycle. The user of this document should note the following:

- Tools and Emulator

- Guidance Documents

- Code Entry (Security IC Embedded Software Delivery)

- 41 **Tools and Emulator:** To aid with the development of the Security IC Embedded Software, specific tools and an emulator configured to simulate the AT90SC28880RCFV2 and Toolbox can be delivered by Inside. The emulator and tools are treated with the same level of protection by Inside as the final IC.

- 42 **Guidance Documents:** To ensure that the end Composite Product is fully protected and that the SFR enforcing mechanisms cannot be tampered with or bypassed, user guidance is delivered in Phase 1 to the Security IC Embedded Software Developer. Delivery procedures are in place to ensure the confidentiality of the sensitive information contained in this documentation set, including secure courier delivery with traceability is followed. Also all parties are covered with NDA before any information is delivered (this also is applicable to Tools and Emulator).

- 43 **Code Entry:** Guidance documents and a delivery tool (SmartACT) are delivered to the Security IC Embedded Software Developer. The guidance document [ACT] describes how to use the SmartACT tool and how to securely transmit the final code to Inside for embedding on the final device. As part of the code delivery a Customer Option Form [COF] is also delivered to the Code entry team in Inside Secure, this gives details of the options that the customer may choose for the AT90SC28880RCFV2 device.

Guidance Documents and Code Entry documents are also delivered as evidence for the AGD class, to allow the ITSEF to use these as part of the search for vulnerabilities during the Vulnerability Assessment part of the evaluation.

#### AT90SC28880RCFV2

# 2 Conformance Claims

45 This chapter contains details the conformance claims for the TOE.

#### 2.1 CC Conformance Claim

- 46 This Security Target claims to be conformant to the Common Criteria Version 3.1, Revision 4, September 2012.

- 47 Furthermore, it claims to be CC Part 2 extended and CC Part 3 conformant. The extended Security Functional Requirements are defined in the Protection Profile.

#### 2.2 Package Claim

48 The TOE is evaluated to EAL5 level augmented with AVA\_VAN.5 and ALC\_DVS.2.

#### 2.3 PP Claim

49 This Security Target is strictly conformant to the Protection Profile BSI-PP-0035 "Security IC Platform Protection Profile"

#### 2.4 PP Refinements

- 50 The refinements to the PP within this security target relate to the Cryptographic Operations. The refinements and additions are taken from "Smartcard Integrated Circuit Augmentations" Version 1.0, March 2002, registered under the German Certification Scheme BSI-AUG-2002 [AUG].

- 51 Refinements are made to the following Security objectives for the environment:

- OE.Plat-Appl

- OE.Resp-Appl

#### 2.5 PP Additions

- 52 The following organisational security policies, security objectives, and security functional requirements have been added.

- P.Add-Functions

- A.Key-Function

- O.Add-Functions

- FCS\_COP.1

#### 2.6 PP Claims Rationale

- 53 The differences between this Security Target and the BSI-PP-0035, that is the addition of:

- Organisational Security Policy

- Assumptions

- Security Objectives for the TOE

- Security Functional Requirements for the TOE

- 54 Do not affect the conformance claim of this Security Target. The Rationale for the additions is given in section 6 and section 7 of this ST.

- 55 For each addition, the appropriate section clearly shows the addition, that is, section 3, Section 4 and section 6.

- 56 Although the PP recommends an EAL4 certification level with augmentations, the TOE claims an EAL5 plus certification level. This ST maintains the conformance to BSI-PP-0035, the rationale for this is given in section 6.

- 57 All the Protection Profile requirements have been shown to be satisfied within this Security Target.

# **3** Security Problem Definition

58 This chapter describes the security aspects of the environment in which the TOE is intended to be used. As this security target is conformant to BSI-PP-0035, this section contains only the relevant details and a summary where applicable. For complete details, refer to the Protection Profile.

# 3.1 Description of Assets

#### Assets regarding the Threats

- 59 The assets (related to standard functionality) to be protected are

- the User Data

- the Security IC Embedded Software, stored and in operation

- the security services provided by the TOE for the Security IC Embedded Software

- 60 The user (consumer) of the TOE places value upon the assets related to high-level security concerns:

- SC1 integrity of User Data and of the Security IC Embedded Software (while being executed/processed and while being stored in the TOE's memories)

- SC2 confidentiality of User Data and of the Security IC Embedded Software (while being processed and while being stored in the TOE's memories)

- SC3 correct operation of the security services provided by the TOE for the Security IC Embedded Software

- 61 According to this Protection Profile there is the following high-level security concern related to security service:

- SC4 deficiency of random numbers.

- 62 To be able to protect these assets the TOE shall protect its security functionality. Therefore, critical information about the TOE shall be protected. Critical information includes:

- logical design data, physical design data, IC Dedicated Software, and configuration data

- Initialisation Data and Pre-personalisation Data, specific development aids, test and characterisation related data, material for software development support, and photomasks

Such information and the ability to perform manipulations assist in threatening the above assets.

#### 3.2 Threats

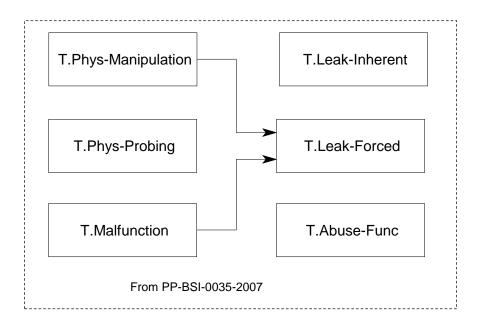

- 63 The threats are listed in PP-BSI-0035, only a summary is provided in this Security target.

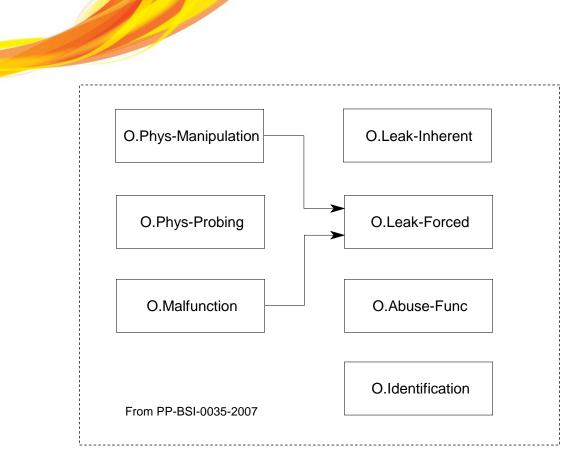

- 64 The standard threats to the TOE are shown in Figure 3.

Figure 3: Standard Threats

65 The threats relating to specific security services are shown in Figure 4.

Figure 4: Threats related to security service

- 66 The Security IC Embedded Software may be required to contribute to preventing the threats. At least it must not undermine the security provided by the TOE. For detail refer to the assumptions regarding the Security IC Embedded Software specified in Section 3.4

- 67 The above security concerns are derived from considering the operational usage by the end-consumer (Phase 7) since

- Phase 1 and the Phases from TOE Delivery up to the end of Phase 6 are covered by assumptions and

- the development and production environment starting with Phase 2 up to TOE Delivery are covered by an organisational security policy.

# 3.3 Organisational Security Policies

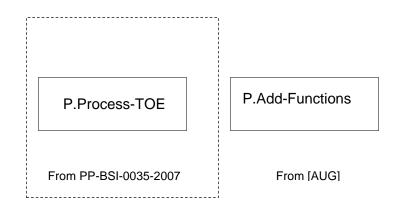

68 The following Figure 5 shows the policies applied in this Security Target.

Figure 5: Policies

- 69 The IC Developer / Manufacturer must apply the policy "Protection during TOE Development and Production (P.Process-TOE)" as specified below.

- P.Process-TOE Protection during TOE Development and Production

An accurate identification must be established for the TOE. This requires that each instantiation of the TOE carries this unique identification.

70 The accurate identification is introduced at the end of the production test in phase 3. Therefore, the production environment must support this unique identification.

71 The IC Developer / Manufacturer must apply the policy "Additional Specific Security Functionality (P.Add-Functions)" as specified below.

P.Add-Functions Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Security IC Embedded Software:

- TDES<sup>a</sup>

- AES <sup>a</sup>

- RSA without CRT <sup>b</sup> \*

- RSA with CRT \*

- PrimeGen (Miller Rabin algorithm) \*

- Secure Hash (SHA) + c

- ECDSA over Zp <sup>‡ d</sup>

- EC-DH over Zp <sup>‡</sup>

- ECDSA over GF(2n) ^ e

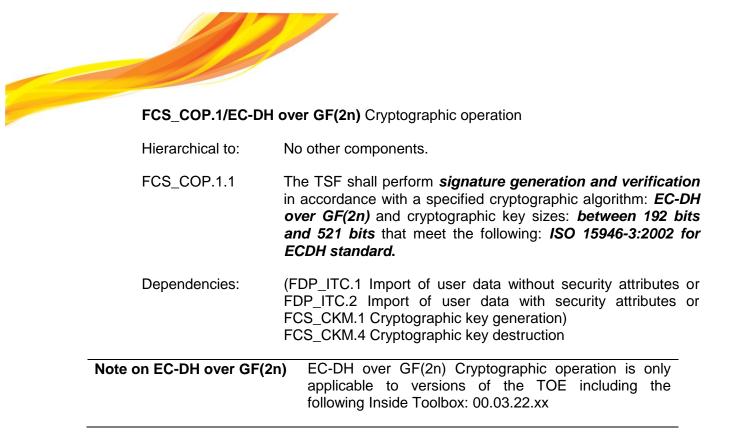

- EC-DH over GF(2n) ^

#### 3.4 Assumptions

- Full details of the assumptions are listed in PP-BSI-0035, only a summary is provided in this Security Target. Full details are given for the additional assumption taken from [AUG].

- Figure 6 shows the assumptions applied in this Security Target.

- <sup>b</sup> The functions marked \* are applicable to toolbox versions 00.03.24.xx, 00.03.20.xx, 00.03.21.xx, 00.03.22.xx

- <sup>c</sup> The functions marked <sup>+</sup> are applicable to toolbox versions 00.03.20.xx, 00.03.21.xx, 00.03.22.xx

- <sup>d</sup> The functions marked <sup>‡</sup> are applicable to toolbox versions 00.03.21.xx, 00.03.22.xx

- <sup>e</sup> The functions marked ^ are applicable to toolbox version 00.03.22.xx

<sup>&</sup>lt;sup>a</sup> The functions TDES and AES are based on a hardware dedicated part of the TOE and are applicable to all versions of the TOE

| A.Process-Sec-IC A.Plat-Appl | A.Key-Function |

|------------------------------|----------------|

| A.Resp-Appl                  |                |

| From PP-BSI-0035-2007        | From [AUG]     |

#### Figure 6: Assumptions

- 74 Appropriate "Protection during Packaging, Finishing and Personalisation (A.Process-Sec-IC)" must be ensured after TOE Delivery up to the end of Phase 6, as well as during the delivery to Phase 7 as specified below.

- A.Process-Sec-IC Protection during Packaging, Finishing and Personalisation

It is assumed that security procedures are used after delivery of the TOE by the TOE Manufacturer up to delivery to the endconsumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

This means that the Phases after TOE Delivery (refer to Section 1.4.3) are assumed to be protected appropriately. For a list of assets to be protected, see below.

- 75 The information and material produced and/or processed by the Security IC Embedded Software Developer in Phase 1 and by the Composite Product Manufacturer can be grouped as follows:

- the Security IC Embedded Software including specifications, implementation and related documentation

- pre-personalisation and personalisation data including specifications of formats and memory areas, test related data

- the User Data and related documentation

- material for software development support

TPG0224C-VIC-09Dec13

- 76 The developer of the Security IC Embedded Software must ensure the appropriate "Usage of Hardware Platform (A.Plat-Appl)" while developing this software in Phase 1 as specified below.

- A.Plat-Appl Usage of Hardware Platform

The Security IC Embedded Software is designed so that the requirements from the following documents are met: (i) TOE guidance documents (refer to the Common Criteria assurance class AGD) such as the hardware data sheet, and the hardware application notes, and (ii) findings of the TOE evaluation reports relevant for the Security IC Embedded Software as documented in the certification report.

77 The developer of the Security IC Embedded Software must ensure the appropriate "Treatment of User Data (A.Resp-Appl)" while developing this software in Phase 1 as specified below.

A.Resp-Appl Treatment of User Data

All User Data is owned by the Security IC Embedded Software. Therefore, it must be assumed that security relevant User Data (especially cryptographic keys) are treated by the Security IC Embedded Software as defined for its specific application context.

- 78 The developer of the Security IC Embedded Software must ensure the appropriate "Usage of key-dependent Functions (A.Key-Function)" while developing this software in Phase 1 as specified below.

- A.Key-Function Usage of Key-dependent Functions

Key-dependent functions (if any) shall be implemented in the Security IC Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

Note that here the routines which may compromise keys when being executed are part of the Security IC Embedded Software. In contrast to this, the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines, which are part of the TOE and (ii) the processing of User Data including cryptographic keys.

# 4 Security Objectives

79 The full details of the Security Objectives are listed in PP-BSI-0035, only a summary is provided in this Security target.

## 4.1 Security Objectives for the TOE

- 80 The user has the following standard high-level security goals related to the assets:

- SG1 maintain the integrity of User Data and of the Security IC Embedded Software (when being executed/processed and when being stored in the TOE's memories) as well as

- SG2 maintain the confidentiality of User Data and of the Security IC Embedded Software (when being processed and when being stored in the TOE's memories).

The Security IC may not distinguish between User Data which is publicly known or requires being confidential. Therefore, the Security IC shall protect the confidentiality and integrity of the User Data, unless the Security IC Embedded Software chooses to disclose or modify it.

In particular, integrity of the Security IC Embedded Software means that it is correctly being executed which includes the correct operation of the TOE's functionality. Though the Security IC Embedded Software (normally stored in the ROM) will in many cases not contain secret data or algorithms, it must be protected from being disclosed. For example, knowledge of specific implementation details may assist an attacker.

- SG3 maintain the correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- 81 These standard high-level security goals in the context of the security problem definition build the starting point for the definition of security objectives as required by the Common Criteria (refer to Figure 7). Note that the integrity of the TOE is a means to reach these objectives.

Figure 7: Standard Security Objectives

- 82 According to this Security Target there is the following high-level security goal related to specific functionality:

- SG4 provide true random numbers.

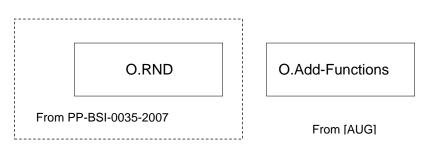

- 83 The additional high-level security considerations are refined below by defining security objectives as required by the Common Criteria (refer to Figure 8).

Figure 8: Security Objectives related to Specific Functionality

#### Security Objectives related to Specific Functionality (referring to SG4)

84 The TOE shall provide "Additional Specific Security Functionality (O.Add-Functions)" [AUG] as specified below.

O.Add-Functions Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Security IC Embedded Software:

- TDES<sup>a</sup>

- AES <sup>a</sup>

- RSA without CRT b \*

- RSA with CRT \*

- PrimeGen (Miller Rabin algorithm) \*

- Secure Hash (SHA) + c

- ECDSA over Zp <sup>‡ d</sup>

- EC-DH over Zp <sup>‡</sup>

- ECDSA over GF(2n) ^ e

- EC-DH over GF(2n) ^

# 4.2 Security Objectives for the Security IC Embedded Software development Environment (not part of TOE)

85 The development of the Security IC Embedded Software is outside the development and manufacturing of the TOE (cf. section 1.4.3). The Security IC Embedded Software defines the operational use of the TOE. This section describes the security objectives for the operational environment enforced by the Security IC Embedded Software.

- <sup>c</sup> The functions marked <sup>+</sup> are applicable to toolbox versions 00.03.20.xx, 00.03.21.xx, 00.03.22.xx

- <sup>d</sup> The functions marked <sup>‡</sup> are applicable to toolbox versions 00.03.21.xx, 00.03.22.xx

- <sup>e</sup> The functions marked ^ are applicable to toolbox version 00.03.22.xx

<sup>&</sup>lt;sup>a</sup> The functions TDES and AES are based on a hardware dedicated part of the TOE and are applicable to all versions of the TOE

<sup>&</sup>lt;sup>b</sup> The functions marked \* are applicable to toolbox versions 00.03.24.xx, 00.03.20.xx, 00.03.21.xx, 00.03.22.xx

#### Phase 1

- 86 The Security IC Embedded Software shall provide "Usage of Hardware Platform (OE.Plat-Appl)" as specified below.

- OE.Plat-Appl Usage of Hardware Platform

To ensure that the TOE is used in a secure manner the Security IC Embedded Software shall be designed so that the requirements from the following documents are met: (i) hardware data sheet for the TOE, (ii) data sheet of the IC Dedicated Software of the TOE, (iii) TOE application notes, other guidance documents, and (iv) findings of the TOE evaluation reports relevant for the Security IC Embedded Software as referenced in the certification report.

The TOE supports cipher schemes as additional specific security functionality. If required the Security IC Embedded Software shall use the cryptographic services of the TOE and their interface as specified. When key-dependent functions implemented in the Security IC Embedded Software are just being executed, the Security IC Embedded Software must provide protection against disclosure of confidential data (User Data) stored and/or processed in the TOE by using the methods described under "Inherent Information Leakage (T.Leak-Inherent)" and "Forced Information Leakage (T.Leak-Forced)" [AUG].

- 87 The Security IC Embedded Software shall provide "Treatment of User Data (OE.Resp-Appl)" as specified below.

- OE.Resp-Appl Treatment of User Data

Security relevant User Data (especially cryptographic keys) are treated by the Security IC Embedded Software as required by the security needs of the specific application context.

For example the Security IC Embedded Software will not disclose security relevant User Data to unauthorised users or processes when communicating with a terminal.

By definition, cipher or plain text data and cryptographic keys are User Data. The Security IC Embedded Software shall treat this data appropriately, use only proper secret keys (chosen from a large key space) as input for the cryptographic function of the TOE and use keys and functions appropriately in order to ensure the strength of the cryptographic operation.

This means that keys are treated as confidential as soon as they are generated. The keys must be unique with a very high probability, as well as cryptographically strong. For example, it must be ensured that it is not practical to derive the private key from a public key if asymmetric algorithms are used. If keys are imported into the TOE and/or derived from other keys, quality and confidentiality must be maintained. This implies that appropriate key management has to be realised in the environment [AUG].

# 4.3 Security Objectives for the operational Environment

#### TOE Delivery up to the end of Phase 6

88 Appropriate "Protection during Packaging, Finishing and Personalisation (OE.Process-Sec-IC)" must be ensured after TOE Delivery up to the end of Phases 6, as well as during the delivery to Phase 7 as specified below.

OE.Process-Sec-IC Protection during composite product manufacturing

Security procedures shall be used after TOE Delivery up to delivery to the end-consumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

This means that Phases after TOE Delivery up to the end of Phase 6 (refer to Section 1.4.3) must be protected appropriately. For a preliminary list of assets to be protected, refer to (Section 3.4, A.Process-Sec-IC).

# 4.4 Security Objectives Rationale

89 Table 1 below shows how the assumptions, threats, and organisational security policies are addressed by the objectives.

| Assumption, Threat or<br>Organisational Security Policy | Security Objective  | Notes                              |

|---------------------------------------------------------|---------------------|------------------------------------|

| A.Plat-Appl                                             | OE.Plat-Appl        | Phase 1                            |

| A.Resp-Appl                                             | OE.Resp-Appl        | Phase 1                            |

| A.Key-Function                                          | OE.Resp-Appl        | Phase 1                            |

|                                                         | OE.Plat-Appl        |                                    |

| P.Process-TOE                                           | O.Identification    | Phase 2 – 3<br>optional<br>Phase 4 |

| A.Process-Sec-IC                                        | OE.Process-Sec-IC   | Phase 5 – 6<br>optional<br>Phase 4 |

| T.Leak-Inherent                                         | O.Leak-Inherent     |                                    |

| T.Phys-Probing                                          | O.Phys-Probing      |                                    |

| T.Malfunction                                           | O.Malfunction       |                                    |

| T.Phys-Manipulation                                     | O.Phys-Manipulation |                                    |

| T.Leak-Forced                                           | O.Leak-Forced       |                                    |

| T.Abuse-Func                                            | O.Abuse-Func        |                                    |

| T.RND                                                   | O.RND               |                                    |

| P.Add-Functions                                         | O.Add-Functions     |                                    |

Table 1: Security Objectives versus Assumptions, Threats or Policies

# 5 Extended Components Definition

- 90 The extended components:

- FCS\_RNG.1

- FMT\_LIM.1

- FMT\_LIM.2

- FAU\_SAS.1

- 91 Are defined within the Protection Profile [PP] that this Security Target is strictly conformant to.

#### AT90SC28880RCFV2

# 6 IT Security Requirements

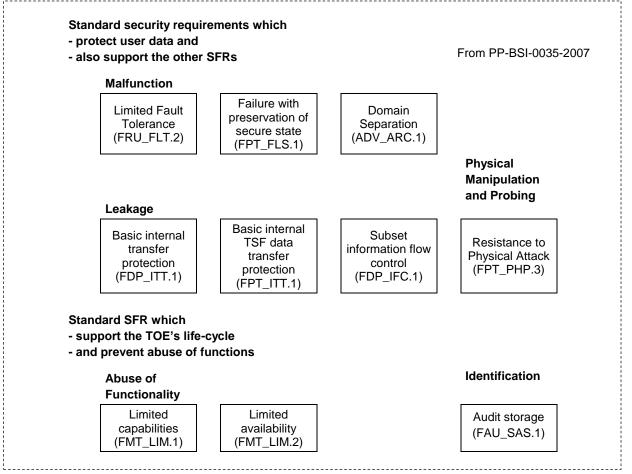

92 The standard Security Requirements are shown in Figure 9. These security components are listed and explained below.

Figure 9: Standard Security Requirements

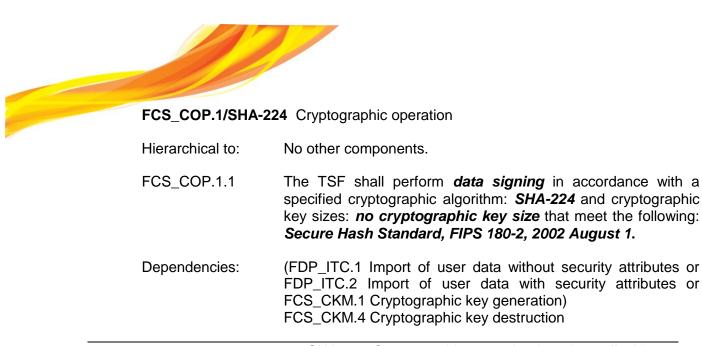

93 The Security Functional Requirements related to Specific Functionality are shown in Figure 10. These security functional components are listed and explained below.

| Standard SFR rela                         | ted to Specific Functionality | /<br>-     |                                           |

|-------------------------------------------|-------------------------------|------------|-------------------------------------------|

| Random<br>Numbers                         | From PP-BSI-0035-2007         | From [AUG] | Cryptography                              |

| Random<br>Number<br>Generatio<br>(FCS_RNG | n                             |            | Cryptographic<br>Operation<br>(FCS_COP.1) |

Figure 10: Security Functional Requirements related to Specific Functionality

# 6.1 Security Functional Requirements for the TOE

94 In order to define the Security Functional Requirements Part 2 of the Common Criteria was used. However, some Security Functional Requirements have been refined (please refer to the Protection Profile [PP]).

#### Malfunctions

- 95 The TOE shall meet the requirement "Limited fault tolerance (FRU\_FLT.2)" as specified below.

- FRU\_FLT.2 Limited fault tolerance

- Hierarchical to: FRU\_FLT.1 Degraded fault tolerance

- FRU\_FLT.2.1 The TSF shall ensure the operation of all the TOE's capabilities when the following failures occur: **exposure to operating** conditions which are not detected according to the requirement Failure with preservation of secure state (FPT\_FLS.1)<sup>a</sup>.

- Dependencies: FPT\_FLS.1 Failure with preservation of secure state.

- Refinement: The term "failure" above also covers "circumstances". The TOE prevents failures for the "circumstances" defined above.

- 96 The TOE shall meet the requirement "Failure with preservation of secure state (FPT\_FLS.1)" as specified below.

- **FPT\_FLS.1** Failure with preservation of secure state

- Hierarchical to: No other components.

- FPT\_FLS.1.1 The TSF shall preserve a secure state when the following types of failures occur: exposure to operating conditions which may not be tolerated according to the requirement Limited fault tolerance (FRU\_FLT.2) and where therefore a malfunction could occur<sup>b</sup>.

Dependencies: No dependencies.

<sup>&</sup>lt;sup>b</sup> TSF\_ENV\_PROTECT details the operating conditions that are not tolerated by the TOE (namely Voltage and temperature out of bounds, and internal frequency following below a defined level). The TOE takes action through TSF\_AUDIT\_ACTION to ensure the TOE fails in a secure state.

<sup>&</sup>lt;sup>a</sup> The TOE operates in a stable way within this operating window, this is verified during the development and manufacturing phase of the life cycle. This is verified by the ITSEF during the ATE Assurance Class analysis.

#### **Abuse of Functionality**

- 97 The TOE shall meet the requirement "Limited capabilities (FMT\_LIM.1)" as specified below (Common Criteria Part 2 extended).

- FMT\_LIM.1 Limited capabilities

- Hierarchical to: No other components.

- FMT\_LIM.1.1 The TSF shall be designed and implemented in a manner that limits their capabilities so that in conjunction with "Limited availability (FMT\_LIM.2)" the following policy is enforced: Deploying Test Features after TOE Delivery does not allow User Data to be disclosed or manipulated, TSF data to be disclosed or manipulated, software to be reconstructed and no substantial information about construction of TSF to be gathered which may enable other attacks<sup>a</sup>.

- Dependencies: FMT\_LIM.2 Limited availability.

- 98 The TOE shall meet the requirement "Limited availability (FMT\_LIM.2)" as specified below (Common Criteria Part 2 extended).

- FMT\_LIM.2 Limited availability

Hierarchical to: No other components.

FMT\_LIM.2.1 The TSF shall be designed and implemented in a manner that limits their availability so that in conjunction with "Limited capabilities (FMT\_LIM.1)" the following policy is enforced: Deploying Test Features after TOE Delivery does not allow User Data to be disclosed or manipulated, TSF data to be disclosed or manipulated, software to be reconstructed and no substantial information about construction of TSF to be gathered which may enable other attacks<sup>b</sup>.

Dependencies: FMT\_LIM.1 Limited capabilities.

<sup>&</sup>lt;sup>a</sup> TSF\_TEST details the Limited capability and availability policy.

<sup>&</sup>lt;sup>o</sup> TSF\_TEST details the Limited capability and availability policy.

99 The TOE shall meet the requirement "Audit storage (FAU\_SAS.1)" as specified below (Common Criteria Part 2 extended).