# AT90SC9608RC Security Target Lite General Business Use

TPG0033C (09 Nov 04)

Atmel makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

The security of any system in which the product is used will depend on the system's security as a whole. Where security or cryptography features are mentioned in this document this refers to features which are intended to increase the security of the product under normal use and in normal circumstances.

All products are sold subject to Atmel's Terms & Conditions of Supply and the provisions of any agreements made between Atmel and the Customer. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and agreements and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Atmel's Terms & Conditions of Supply is available on request.

© Atmel Corporation 2004

| Section 1 | AT90SC9608RC Security Target Lite           |    |

|-----------|---------------------------------------------|----|

|           | 1.1 Identification                          | 9  |

|           | 1.2 Overview                                | 9  |

|           | 1.3 Common Criteria Conformance Claim       | 10 |

|           | 1.4 Document Objective                      | 10 |

|           | 1.5 Document Structure                      | 10 |

|           | 1.6 Scope and Terminology                   | 11 |

|           | 1.7 References                              | 11 |

|           | 1.8 Revision History                        | 12 |

|           |                                             |    |

| Section 2 | Target of Evaluation Description            | 13 |

|           | 2.1 Product Type                            | 13 |

|           | 2.2 Smartcard Product Life-cycle            | 15 |

|           | 2.3 TOE Environment                         | 17 |

|           | 2.4 TOE Logical Phases                      | 18 |

|           | 2.5 TOE Intended Usage                      | 19 |

|           | 2.6 General IT Features of the TOE          | 21 |

| Section 3 | TOE Security Environment                    | 23 |

|           | 3.1 Assets                                  | 23 |

|           | 3.2 Assumptions                             | 23 |

|           | 3.3 Threats                                 | 25 |

|           | 3.4 Organizational Security Policies        | 29 |

| Section 4 | Security Objectives                         | 31 |

|           | 4.1 Security Objectives for the TOE         | 31 |

|           | 4.2 Security Objectives for the Environment |    |

| Section 5  | TOE Security Functional Requirements                                   | 39 |

|------------|------------------------------------------------------------------------|----|

|            | 5.1 Functional Requirements Applicable to Phase 3 Only (Testing Phase) | 39 |

|            | 5.2 Functional Requirements Applicable to Phases 3 to 7                | 41 |

|            | 5.3 TOE Security Assurance Requirements                                | 46 |

| Section 6  | TOE Summary Specification                                              | 49 |

|            | 6.1 TOE Security Functions                                             | 49 |

|            | 6.2 TOE Assurance Measures                                             | 55 |

| Section 7  | Protection Profile Claims                                              |    |

|            | 7.1 Protection Profile Reference                                       | 59 |

|            | 7.2 Protection Profile Refinements                                     | 59 |

|            | 7.3 Protection Profile Additions                                       | 59 |

| Appendix A | Glossary                                                               |    |

|            | A.1 Terms                                                              | 61 |

|            | A O Abbassisticas                                                      | 00 |

| Figure 2-1 | Smartcard Product Life Cycle | 16 |

|------------|------------------------------|----|

| -IOUTE 2-1 | Smarrcard Product Life Cycle | 16 |

| Table 2-1 | Smartcard Product Life-cycle                                      | 15 |

|-----------|-------------------------------------------------------------------|----|

| Table 2-2 | Phases 4 to 7 Product Users                                       | 20 |

| Table 3-1 | Threats and Phases                                                | 28 |

| Table 5-1 | IFCSF-Policy                                                      | 44 |

| Table 6-1 | Relationship Between Security Requirements and Security Functions | 54 |

| Table 6-2 | Relationship Between Assurance Requirements and Measures          | 57 |

#### AT90SC9608RC Security Target Lite

#### 1.1 Identification

Title: AT90SC9608RC Security Target Lite [ST\_Lite]

This Security Target Lite has been constructed with Common Criteria (CC) Version 2.1.

#### 1.2 Overview

1

2

4

5

This Security Target Lite [ST\_Lite] is for a microcontroller (MCU) device with security features. The device is a member of a family of single chip MCU devices which are intended for use within Smartcard products. The family codename is AVR ASL4 and the 'parent' device of the family, from which other family members will be derived, is the AT90SC19264RC.

The AT90SC9608RC MCU device (AT578A7) is being evaluated against the CC Smartcard Integrated Circuit Protection Profile PP/9806 to Evaluation Assurance Level 4 (EAL4) augmented of AVA\_VLA.4 under the Common Criteria maintenance scheme. Atmel Smart Card ICs, a division of ATMEL Corporation, is the developer and the sponsor for the AVR ASL4 evaluations.

The devices in the AVR ASL4 family are based on the AVR RISC family of single-chip microcontroller devices. The AVR RISC family, with designed-in security features, is based on the industry-standard AVR low-power HCMOS core and gives access to the powerful instruction set of this widely used device. AVR ASL4 devices are equipped with Flash, RAM, ROM and EEPROM, cryptographic coprocessors, and a host of security features to protect device assets, making them suitable for a wide range of smartcard applications.

7

#### 1.3 Common Criteria Conformance Claim

This Security Target Lite is conformant to parts 2 and 3 of the Common Criteria, V2.1, as follows:

- Part 2 conformant: the security functional requirements are based on those identified in part 2 of the Common Criteria.

- Part 3 augmented conformant: the security assurance requirements, including those used in the augmentation, are based on those in part 3 of the Common Criteria.

#### 1.4 Document Objective

The purpose of this document is to satisfy the Common Criteria (CC) requirements for a Security Target Lite; in particular, to specify the security requirements and functions, and the assurance requirements and measures, in accordance with Protection Profile PP/9806, Smartcard Integrated Circuit V2.0, against which the AVR ASL4 devices will be evaluated.

#### 1.5 Document Structure

Section 1 Introduces the Security Target Lite and includes sections on terminology and references.

Section 2 Contains the product description and describes the TOE as an aid to the understanding of its security requirements and addresses the product type, the intended usage and the general features of the TOE.

- Section 3 Describes the TOE security environment.

- Section 4 Describes the required security objectives.

- Section 5 Describes the TOE security functional requirements and the security assurance requirements.

- Section 6 Describes the TOE security functions.

- Section 7 Describes the protection profile (PP) claims.

- Appendix A Provides a glossary of terms and abbreviations used in this document.

#### 1.6 Scope and Terminology

This document is based on the AT90SC9608RC Technical Data Sheet [TD].

The term *Target of Evaluation* (TOE) is standard CC terminology and refers to the product being evaluated, the AT90SC9608RC MCU device in this case. The TOE is subject to hardware evaluation only. Downloaded test software will be used for evaluation purposes but is outside the scope of the TOE. Description of how to use the security features can be found in [TD].

Security objectives are defined herein with labels in the form O.xx\_xx. These labels are used elsewhere for reference. Similarly, threats, assumptions and organizational security policy are defined with labels of the form T.xx\_xx, A.xx\_xx, and P.xx\_xx respectively.

Hexadecimal numbers are prefixed by \$, e.g. \$FF is 255 decimal. Binary numbers are prefixed by %, e.g. %0001 1011 is decimal 27. An integer value may be expressed as a hexadecimal, binary or decimal number, whichever form is the most convenient.

#### 1.7 References

9

10

11

12

The following list refers to the latest revision of the documents. Contact your local Atmel Sales office for further information.

| ďΓ | M |         | AT90SC9608RC     | Strongth of | Cocurity | Eupotions /  | \nalveid         |

|----|---|---------|------------------|-------------|----------|--------------|------------------|

|    | ш | <br>SUF | I A I 30303000NC | Suengui oi  | Security | FullClions A | <b>Allalyola</b> |

- [STI] Standard Test Interface

- [TD] AT90SC9608RC Technical Data (1581)

- [TestROMDD] AT90SC9608RC Engineering Evaluation Test Software Detailed Description

- [TestROMUG] AT90SC9608RC Engineering ROM User Guide

- [TMRE2] AT90SC9608RC Test Software Specification Test Description

- [TMR-USER] Test Software Specification User Guide

- [TBX] Toolbox V2.1 SC16 Crypto-Coprocessor Library (TPR0096)

#### AT90SC9608RC Security Target Lite

### 1.8 Revision History

| Rev | Date      | Description                                                                                      | Originator |

|-----|-----------|--------------------------------------------------------------------------------------------------|------------|

| Α   | 24 Nov 03 | Initial release. Based on the Common Criteria Version 1.0.                                       | Atmel, EKB |

| В   | 30 Apr 04 | Updated with evaluator comments.                                                                 | Atmel, EKB |

| С   | 09 Nov 04 | Updated with additional cryptographic information. And removed reference to revision of silicon. | Atmel, EKB |

#### Target of Evaluation Description

This part of the Security Target Lite [ST\_Lite] describes the Target of Evaluation (TOE) as an aid to the understanding of its security requirements and address the product type, the intended usage and the general features of the TOE.

#### 2.1 Product Type

13

15

16

17

The TOE is the single chip microcontroller unit to be used in a smartcard product, independent of the physical interface and the way it is packaged. Specifically, the TOE is the AT90SC9608RC device (AT578A7) from the AVR ASL4 family of smartcard devices. Generally, a smartcard product may include other optional elements (such as specific hardware components, batteries, capacitors, antennae) but these are not in the scope of this Security Target Lite.

The devices in the AVR ASL4 family are based on ATMEL's AVR RISC family of single-chip microcontroller devices. The AVR RISC family, with designed-in security features, is based on the industry-standard AVR RISC low-power HCMOS core and gives access to the powerful instruction set of this widely used device. Different AVR ASL4 family members offer various options. The AVR ASL4 family of devices are designed in accordance with the ISO standard for integrated circuit cards (ISO 7816), where appropriate.

Although the TOE evaluation is hardware only, the TOE requires embedded software to test the device and demonstrate certain security characteristics during the development phase. In the end-usage phase there will be no embedded test software in the TOE. Test software will be downloaded into the device EEPROM and be fully erased before devices leave the test environment. This this test software is only used for the testing phase of the TOE life cycle and is outwith the scope of the evaluation. Test mode is disabled by wafer saw.

- The TOE widely uses ATMEL high density non volatile memories: it features 96K bytes of AVR ROM program memory, 8K bytes of EEPROM program/data memory, 3K bytes of static RAM memory.

- The EEPROM includes 128 bytes of One Time Programmable (OTP) memory (64 bytes are byte-addressable; 64 bytes are bit-addressable) and a 384-byte bit-addressable area.

- The EEPROM contains both Atmel and customer specific data.

- The TOE includes security logic comprising detectors which monitor voltage, frequency and temperature.

#### AT90SC9608RC Security Target Lite

| 21 | The TOE is equipped with logic peripherals including 2 timers, 2 serial ports, an |

|----|-----------------------------------------------------------------------------------|

|    | ISO7816 interface and an ISO7816 controller.                                      |

- The TOE contains a basic crypto library (Toolbox V2.1) with cryptographic primitives (such as modular exponentiation) provided by Atmel [TBX]. Within the scope of the TOE are the following commands SHA-1, Modular Exponentiation, fast Modular Exponentiation, and Modular Exponentiation with CRT. Further information can not be given in the Security Target Lite due to its secure nature.

- The TOE includes a powerful Firewall that protects all memories, peripheral and IO register accesses. This Firewall defines the user modes Supervisor mode and Nonsupervisor mode, and many different address spaces.

#### 2.2 Smartcard Product Life-cycle

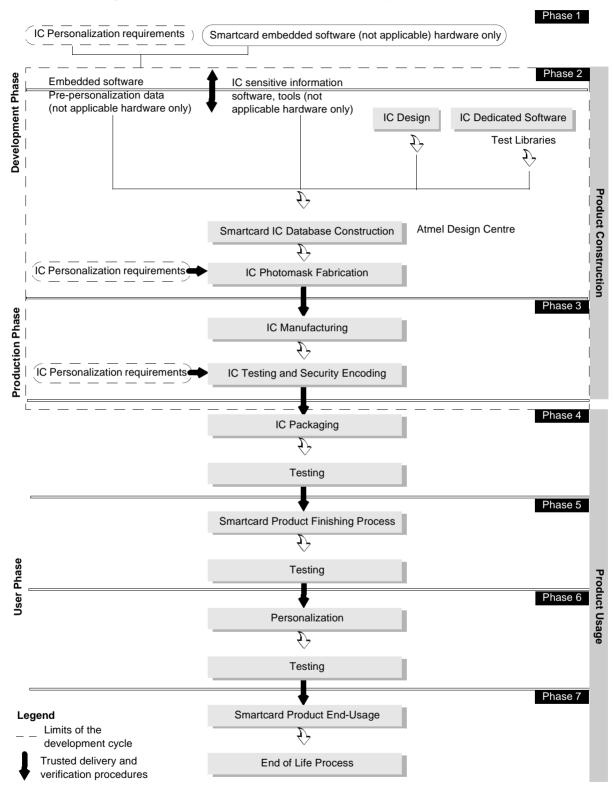

The smartcard product life-cycle consists of 7 phases where the following authorities are involved.

Table 2-1 Smartcard Product Life-cycle

24

| Phase 1 | Smartcard software development      | The smartcard software developer is in charge of the smartcard embedded software development and the specification of IC pre-personalization requirements,                                                                                                                                                                                                                                                                    |

|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase 2 | IC Development                      | The IC designer designs the IC, develops IC dedicated software, provides information, software or tools to the smartcard software developer, and receives the software from the developer, through trusted delivery and verification procedures. From the IC design, IC dedicated software and smartcard embedded software, the IC designer constructs the smartcard IC database, necessary for the IC photomask fabrication. |

| Phase 3 | IC manufacturing and testing        | The IC manufacturer is responsible for producing the IC through three main steps:  IC manufacturing IC testing IC pre-personalization                                                                                                                                                                                                                                                                                         |

| Phase 4 | IC packaging and testing            | The IC packaging manufacturer is responsible for the IC packaging and testing.                                                                                                                                                                                                                                                                                                                                                |

| Phase 5 | Smartcard product finishing process | The smartcard product manufacturer is responsible for the smartcard product finishing process and testing.                                                                                                                                                                                                                                                                                                                    |

| Phase 6 | Smartcard personalization           | The personalizer is responsible for the smartcard personalization and final tests. Other application software may be loaded onto the chip at the personalization process.                                                                                                                                                                                                                                                     |

| Phase 7 | Smartcard end-usage                 | The smartcard issuer is responsible for the smartcard product delivery to the smartcard end-user, and the end of life process.                                                                                                                                                                                                                                                                                                |

The limits of the evaluation correspond to phases 2 and 3, including the phase 1 delivery and verification procedures and the TOE delivery to the IC packaging manufacturer; procedures corresponding to phases 4, 5, 6 and 7 are outside the scope of this document.

Nevertheless, in certain cases, it would be of great interest to include the phase 4 (IC packaging and testing), within the limits of the TOE. However, for the time being, this option remains outside the scope of this document.

25

26

Figure 2-1 illustrates the smartcard product life cycle.

Figure 2-1 Smartcard Product Life Cycle

16 of 64 General Business Use TPG0033C (09 Nov 04)

28

29

31

32

33

34

35

These different phases may be performed at different sites; procedures on the delivery process of the TOE shall exist and be applied for every delivery within a phase or between phases. This includes any kind of delivery performed from phase 1 to phase 7, including:

- Intermediate delivery of the TOE or the TOE under construction within a phase

- Delivery of the TOE or the TOE under construction from one phase to the next

These procedures shall be compliant with the assumptions [A\_DLV] developed in Section 3.2.2.

#### 2.3 TOE Environment

30 Considering the TOE, three types of environments are defined:

- Development environment corresponding to phase 2

- Production environment corresponding to phase 3

- User environment, from phase 4 to phase 7

#### 2.3.1 TOE Development Environment

To assure security, the environment in which the development takes place is made secure with controllable accesses having traceability. Access to the development building is strictly monitored by security staff. Visitors must sign a log book and record the time of arrival and time of departure to the building. All visitors are escorted by authorized personnel at all times. All authorized personnel involved fully understand the importance and the rigid implementation of the defined security procedures.

The development begins with the TOE's specification. All parties in contact with sensitive information are required to abide by Non-Disclosure Agreements.

Reticles and photomasks are generated from the verified IC database. The reticles and photomasks are then shipped securely to the wafer fab processing facilities.

#### 2.3.2 TOE Production Environment

Production starts within the ATMEL Wafer Fabrication plant; here the silicon wafers undergo diffusion processing in 25-wafer lots. Computer tracking at wafer level throughout the process is achieved by a based batch tracking system.

The tracking system is an on-line manufacturing tracking system which monitors the progress of the wafers through the fabrication cycle. After fabrication the wafers are sent to ATMEL Test Fab where they are thinned to a pre-specified thickness and tested. ATMEL EKB test the TOE to assure conformance with the device specification. During the IC testing, security encoding is performed where some of the EEPROM bytes are programmed with the unique traceability information, and the customer software is loaded in the EEPROM if required.

#### AT90SC9608RC Security Target Lite

41

43

The wafers are inked to separate the functional ICs from the non-functional ICs. Finally, the wafers are sawn and then shipped to the customer.

#### 2.3.3 TOE User Environment

- The TOE user environment is the environment of phases 4 to 7.

- 38 At phases 4, 5, and 6, the TOE user environment is a controlled environment.

- Following the sawing step, the wafers are split into individual dies. The good ICs are assembled into modules in a module assembly plant.

- Further testing is carried out followed by the shipment of the modules to the smartcard product manufacturer (embedder) by means of a secure carrier.

- Additional testing occurs followed by smartcard personalization, retesting and then delivery to the smartcard issuer.

#### **End-user environment (Phase 7)**

- Smartcards are used in a wide range of applications to assure authorized conditional access. Examples of such are Pay-TV, Banking Cards, Portable communication SIM cards, Health cards, Transportation cards.

- Therefore, the user environment covers a wide spectrum of very different functions, thus making it difficult to avoid or monitor any abuse of the TOE.

#### 2.4 TOE Logical Phases

During its construction usage, the TOE may be under several life logical phases. These phases are sorted under a logical controlled sequence. The change from one phase to the next shall be under the TOE control.

64

#### 2.5 TOE Intended Usage

The TOE can be incorporated in several applications such as:

- Banking and finance market for credit/debit cards, electronic purse (stored value cards) and electronic commerce.

- Network based transaction processing such as mobile phones (GSM SIM cards), pay-TV (subscriber and pay-per-view cards), communication highways (Internet access and transaction processing).

- Transport and ticketing market (access control cards).

- Governmental cards (ID-cards, healthcards, driver license etc).

- Multimedia commerce and Intellectual Property Rights protection.

During the phases 1, 2, 3, the product is being developed and produced. The administrators are the following:

The IC designer:

46

Authorized staff who work for the developer, and who design the MCU (such development staff are trusted and privileged users).

■ The IC manufacturer:

Authorized staff who work for the developer and who manufacture and test the MCU (such manufacturing staff are trusted and priviliged users).

The smartcard dedicated software developer:

Authorized staff who work for the developer and who develop the dedicated test software and crypto libraries (such development staff are trusted and priviliged users).

#### Table 2-2 lists the users of the product during phases 4 to 7.

Table 2-2 Phases 4 to 7 Product Users

#### Phase 4

- Packaging manufacturer (administrator)

- Smartcard embedded software developer

- System integrator, such as the terminal software developer

#### Phase 5

- Smartcard product manufacturer (administrator)

- Smartcard embedded software developer

- System integrator, such as the terminal software developer

#### Phase 6

- Personalizer (administrator)

- Customers who, before manufacture, determine the MCU's mask options and the initial memory contents (i.e. the application program), and who, after manufacture, incorporate the MCU into devices. Customers are trusted and privileged users.

- Smartcard issuer (administrator).

- Smartcard embedded software developer.

- System integrator, such as the terminal software developer.

#### Phase 7

- Smartcard issuer (administrator)

- Smartcard end-user, who use devices incorporating the MCU.

End-users are not trusted and may attempt to attack the MCU.

- Smartcard software developer.

- System integrator, such as the terminal software developer.

The IC manufacturer and the smartcard product manufacturer may also receive ICs for analysis, should problems occur during the smartcard usage.

#### The MCU may be used in the following modes:

- a) Test mode, in which the MCU runs under the control of dedicated test software written to EEPROM via a test interface, and in conjunction with stimulus provided by an external test system. This mode is intended to be used solely by authorized development staff.

- User mode, in which the MCU runs under control of the smartcard embedded software. It is intended that customers and end-users will always use the MCU in User mode.

- During the initial part of the manufacturing process, the MCU is set to Test mode. Authorized development staff then test the MCU. After testing, Test mode is permanently disabled and the MCU is set to User mode.

- If a faulty MCU is returned from the field then analysis can only be done in User mode because Test mode is inhibited prior to devices going to the field.

- 51 There is no intermediate mode for fault analysis. The only modes of operation are those stated in paragraph 48.

- Once manufactured, the MCU operates by executing the smartcard embedded software, which is stored in AVR ROM. The contents of the AVR ROM cannot be modified, whereas the contents of the EEPROM can, in general, be written to or erased, under the control of the smartcard embedded software.

- The EEPROM includes OTP bytes, which can be used to store security-related information such as cryptographic keys. The OTP bytes cannot be erased in User mode.

- The FireWall (Memories and Peripherals Protection Unit) allows the smartcard embedded software to prevent read/write/execute access to (parts of) AVR ROM, EEPROM, RAM, Crypto ROM and peripherals from EEPROM.

- The ISO7816 compliant I/O ports can be used to pass data to or from the MCU. The application program determines how to interpret the data.

#### 2.6 General IT Features of the TOE

The TOE IT functionalities consist of data storage and processing such as:

- Arithmetic functions (e.g. incrementing counters in electronic purses, calculating currency conversion in electronic purses)

- Data communication

- Cryptographic operations (e.g. data encryption, digital signature verification)

53

55

#### **TOE Security Environment**

57

60

61

62

This section describes the security aspects of the environment in which the TOE is intended to be used, and addresses the description of the assumptions, the assets to be protected, the threats, and the organizational security policies.

#### 3.1 Assets

Assets are security relevant elements of the TOE that include the:

- Application data of the TOE comprising the IC pre-personalization requirements, such as the AVR ROM, EEPROM, the Crypto ROM and OTP contents.

- Smartcard embedded software

- IC specification, design, development tools and technology

- Therefore, the TOE itself is an asset.

- Assets must be protected in terms of confidentiality, integrity and availability.

#### 3.2 Assumptions

It is assumed that this section concerns the following items:

- Due to the definition of the TOE limits, any assumption for the smartcard software development (phase 1 is outside the scope of the TOE)

- Any assumption from phases 4 to 7 for the secure usage of the TOE, including the TOE trusted delivery procedures

Security is always dependent on the whole system: the weakest element of the chain determines the total system security. Assumptions described hereafter must be considered for a secure system using smartcard products:

- Assumptions on phase 1

- Assumptions on the TOE delivery process (phases 4 to 7)

- Assumptions on phases 4-5-6

- Assumptions on phase 7

#### 3.2.1 Assumptions on Phase 1

A.SOFT\_ARCHI The smartcard embedded software shall be designed in a

secure manner, that is focusing on integrity of program and

data.

A.DEV ORG Procedures dealing with physical, personnel, organizational,

technical measures for the confidentiality and integrity of smartcard embedded software (e.g. source code and any associated documents) and IC designer proprietary

information (tools, software, documentation.) shall exist and

be applied in software development.

#### 3.2.2 Assumptions on the TOE Delivery Process (Phases 4 to 7)

Procedures shall guarantee the control of the TOE delivery and storage process and conformance to its objectives as described in the following assumptions.

A.DLV PROTECT Procedures shall ensure protection of TOE material and

information under delivery and storage.

A.DLV\_AUDIT Procedures shall ensure that corrective actions are taken in

case of improper operation in the delivery process and

storage.

A.DLV\_RESP Procedures shall ensure that people dealing with the

procedure for delivery have got the required skill.

#### 3.2.3 Assumptions on Phases 4 to 6

A.USE\_TEST It is assumed that appropriate functionality testing of the IC is

used in phases 4, 5 and 6.

A.USE\_PROD It is assumed that security procedures are used during all

manufacturing and test operations through phases 4, 5, 6 to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy,

modification, retention, theft or unauthorized use).

#### 3.2.4 Assumptions on Phase 7

A.USE\_DIAG It is assumed that secure communication protocols and

procedures are used between smartcard and terminal.

A.USE\_SYS It is assumed that the integrity and confidentiality of sensitive

data stored/handled by the system (terminals,

communications...) is maintained.

63

#### 3.3 Threats

64

65

66

67

The TOE as defined in Section 2 is required to counter the threats described hereafter; a threat agent wishes to abuse the assets either by functional attacks, environmental manipulations, specific hardware manipulations or by any other types of attacks.

Threats have to be split in:

- Threats against which specific protection within the TOE is required (class I),

- Threats against which specific protection within the environment is required (class II).

#### 3.3.1 Unauthorized Full or Partial Cloning of the TOE

T.CLON Functional cloning of the TOE (full or partial) appears to be

relevant to any phases of the TOE life-cycle, from phase 1 to

phase 7.

Generally, this threat is derived from specific threats combining unauthorized disclosure, modification or theft of

assets at different phases.

#### 3.3.2 Threats on Phase 1 (Delivery and Verification Procedures)

During phase 1, three types of threats have to be considered:

- a) Threats on the smartcard's embedded software and its environment of development, such as:

- Unauthorized disclosure

- Modification or theft of the smartcard embedded software and any additional data at phase 1.

Considering the limits of the TOE, these previous threats are outside the scope of this document.

- b) Threats on the assets transmitted from the IC designer to the smartcard software developer during the smartcard development.

- c) Threats on the smartcard embedded software and any additional application data transmitted during the delivery process from the smartcard embedded software developer to the IC designer.

The previous types b and c threats are described hereafter.

T.DIS\_INFO Unauthorized disclosure of the assets delivered by the IC

designer to the smartcard software developer such as sensitive information on IC specification, design and

technology, software and tools if applicable.

T.DIS\_DEL Unauthorized disclosure of the smartcard embedded

software and any additional application data (such as IC prepersonalization requirements) during the delivery process to

the IC designer.

T.MOD DEL Unauthorized modification of the smartcard embedded

software and any additional application data (such as IC prepersonalization requirements) during the delivery process to

the IC designer.

T.T DEL Theft of the smartcard embedded software and any

additional application data (such as IC pre-personalization requirements) during the delivery process to the IC designer.

#### 3.3.3 Threats on Phases 2 to 7

During these phases, the assumed threats could be described in three types:

- Unauthorized disclosure of assets

- Theft or unauthorized use of assets

- Unauthorized modification of assets

#### **Unauthorized disclosure of assets**

70

This type of threats covers unauthorized disclosure of assets by attackers who may possess a wide range of technical skills, resources and motivation. Such attackers may also have technical awareness of the product.

T.DIS\_DESIGN Unauthorized disclosure of IC design.

This threat covers the unauthorized disclosure of proprietary elements such as IC specification, IC design, IC technology detailed information, IC hardware security mechanisms

specifications.

T.DIS\_SOFT Unauthorized disclosure of smartcard embedded software

and data such as access control, authentication system, data protection system, memory partitioning, cryptographic

programs.

T.DIS DSOFT Unauthorized disclosure of IC dedicated software.

This threat covers the unauthorized disclosure of IC dedicated software including security mechanisms

specifications and implementation.

T.DIS\_TEST Unauthorized disclosure of test information such as full

results of IC testing including interpretations.

T.DIS TOOLS Unauthorized disclosure of development tools.

This threat covers potential disclosure of IC development tools and testing tools (analysis tools, microprobing tools).

T.DIS PHOTOMASK Unauthorized disclosure of photomask information, used for

photoengraving during the silicon fabrication process.

#### Theft or unauthorized use of assets

Potential attackers may gain access to the TOE and perform operations for which they are not authorized. For example, such attackers may personalize the product in an unauthorized manner, or try to gain fraudulous access to the smartcard system.

T.T\_SAMPLE Theft or unauthorized use of TOE silicon samples, for

example, bond out chips.

T.T\_PHOTOMASK Theft or unauthorized use of TOE photomasks.

T.T\_PRODUCT Theft or unauthorized use of smartcard products.

#### Unauthorized modification of assets

The TOE may be subjected to different types of logical or physical attacks which may compromise security. Due to the intended usage of the TOE (the TOE environment may be hostile), the TOE security parts may be bypassed or compromised reducing the integrity of the TOE security mechanisms and disabling their ability to manage the TOE security. This type of threat includes the implementation of malicious trojan horses.

T.MOD\_DESIGN Unauthorized modification of IC design.

This threat covers the unauthorized modification of IC specification, IC design including IC hardware security

mechanisms specifications and realization.

T.MOD\_PHOTOMASK Unauthorized modification of TOE photomasks.

T.MOD\_DSOFT Unauthorized modification of IC dedicated software

including modification of security mechanisms.

T.MOD SOFT Unauthorized modification of smartcard embedded

software and data.

71

72

Table 3-1 indicates the relationships between the smartcard phases and the threats.

Table 3-1 Threats and Phases

| Threats                           | Phase 1  | Phase 2  | Phase 3    | Phase 4 | Phase 5 | Phase 6 | Phase 7 |

|-----------------------------------|----------|----------|------------|---------|---------|---------|---------|

| Functional cloning                |          |          |            |         |         |         |         |

| T.CLON                            | Class II | Class II | Class I/II | Class I | Class I | Class I | Class I |

| Unauthorized disclosure of asse   | ets      |          |            |         |         |         |         |

| T.DIS_INFO                        | Class II |          |            |         |         |         |         |

| T.DIS_DEL                         | Class II |          |            |         |         |         |         |

| T.DIS_SOFT                        |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.DIS_DSOFT                       |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.DIS_DESIGN                      |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.DIS_TOOLS                       |          | Class II | Class II   |         |         |         |         |

| T.DIS_PHOTOMASK                   |          | Class II | Class II   |         |         |         |         |

| T.DIS_TEST                        |          |          | Class I/II | Class I | Class I | Class I |         |

| Theft or unauthorized use of as   | sets     |          |            | •       |         | •       |         |

| T.T_DEL                           | Class II |          |            |         |         |         |         |

| T.T_SAMPLE                        |          | Class II | Class I/II | Class I | Class I |         |         |

| T.T_PHOTOMASK                     |          | Class II | Class II   |         |         |         |         |

| T.T_PRODUCT                       |          |          | Class I/II | Class I | Class I | Class I | Class I |

| Unauthorized modification threats |          |          |            |         |         |         |         |

| T.MOD_DEL                         | Class II |          |            |         |         |         |         |

| T.MOD_SOFT                        |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.MOD_DSOFT                       |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.MOD_DESIGN                      |          | Class II | Class I/II | Class I | Class I | Class I | Class I |

| T.MOD_PHOTOMASK                   |          | Class II | Class II   |         |         |         |         |

#### 3.4 Organizational Security Policies

An organizational security policy is mandatory for the smartcard product usage. The specifications of organizational security policies essentially depend on the applications in which the TOE is incorporated.

However, it was found relevant to address the following organizational security policy with the TOE because most of the actual Smart Card secure applications make use of cryptographic standards.

#### P.CRYPTO

75

Cryptographic entities, data authentication, and approval functions must be in accordance with ISO, associated industry, or organizational standards or requirements.

Various cryptographic algorithms and mechanisms, such as triple DES, AES, RSA, MACs, and Digital Signatures, are accepted international standards. These, or others in accordance with industry or organizational standards of similar maturity and definition, should be used for all cryptographic operations in the TOE.

These cryptographic operations are used for instance to support establishment and control of a trusted channel between the TOE and the outside environment.

To support these cryptographic functions, the TOE should supply Random Number Generation (RNG) with sufficient unpredictability and entropy. The TOE shall ensure that no information about the produced random numbers is available to an attacker since they might be used for instance to generate cryptographic keys.

#### **Security Objectives**

The security objectives of the TOE cover principally the following aspects:

- Integrity and confidentiality of assets

- Protection of the TOE and associated documentation during development and production phases

#### 4.1 Security Objectives for the TOE

The TOE shall use state of art technology to achieve the following IT security objectives:

#### **O.TAMPER**

77

## The TOE must prevent physical tampering with its security critical parts.

The TOE must provide protection against disclosure of User data, against disclosure/reconstruction of the Smartcard Embedded Software or against disclosure of other critical operational information.

This includes protection against direct micro-probing of signals not connected to bonding pads, but also other contact or contactless probing techniques such as laser probing or electromagnetic sensing. Most of these techniques require a prior reverse engineering of parts of the device to understand its architecture and its security functions.

This also includes protection against inherent information leakage (for example shape of signals, power consumption) on the device external interfaces (for example clock, supply, I/O lines) that could be used to disclose confidential data, as well as forced information leakage caused by induced malfunction or physical manipulation

O.CLON

## The TOE functionality needs to be protected from cloning.

The TOE must include means to prevent an attacker from reproducing the smartcard functionality. Most of these techniques require a prior reverse engineering of parts of the device to understand its architecture and its security functions.

O.OPERATE

## The TOE must ensure the continued correct operation of its security functions.

The TOE must include protection against the use of stolen silicon samples or products that would ease an attacker gaining fraudulous access to the smartcard system.

The TOE must also provide mechanisms to avoid the unauthorized modification of the security functions or software and data, by using the device test commands for instance, or by using uncontrolled/unauthentified software access to memories.

The TOE must prevent its operation outside the normal operating conditions where reliability and secure operation has not been proven or tested. This is to prevent errors. The environmental conditions may include voltage, clock frequency, temperature, or external energy fields

O.FLAW

## The TOE must not contain flaws in design, implementation or operation.

The TOE design must include protection against modification of its security mechanisms (for example detectors or memory protections) that would lead to bypass or reduce their integrity, and therefore open security holes that could be used to access embedded software and data.

The TOE design must also provide protection against modification of its embedded software that would lead to bypass or reduce the integrity of some software controlled security mechanisms (for example memory areas definition), and therefore open security holes that could be used to access embedded software and data.

O.DIS\_MECHANISM

# The TOE shall ensure that the hardware security mechanisms are protected against unauthorized disclosure.

The TOE must be designed and fabricated so that it requires a high combination of complex equipment, knowledge, skill and time to derive detailed designed information or other information which could be used to compromise security through physical attacks.

O.DIS\_MEMORY

The TOE shall ensure that sensitive information stored in memories is protected against unauthorized access.

The TOE must provide protection against unauthorized access to embedded software and data stored in memories, either using test commands, or by some embedded software (for instance a non-supervisor user application) that would try to dump the memories protected by the Firewall programmation (for instance the supervisor program and/or data), or even by some physical attacks.

O.MOD\_MEMORY

The TOE shall ensure that sensitive information stored in memories is protected against any corruption or unauthorized modification.

The TOE must provide protection against unauthorized access to embedded software and data stored in memories, either using test commands, or by some embedded software (for instance a non-supervisor user application) that would try to modify the memories protected by the Firewall programmation (for instance the supervisor program and/or data), or even by some physical attacks.

O.CRYPTO

Cryptographic capability shall be available for users to maintain integrity and confidentiality of sensitive data.

The TOE must provide hardware implementation of some cryptographic algorithms that can be used by the embedded software in conjunction with appropriate counter-measure to achieve cryptographic operations (for instance encryption, decryption, integrity checking, signature, key generation, for algorithms such as DES, TDES, RSA, SHA-1, DSA, Elliptic Curves, ...).

These cryptographic operations are used for instance to support establishment and control of a trusted channel between the TOE and the outside environment, or protect confidential data stored in the TOE memories.

The TOE must also provide random number generation and ensure the cryptographic quality of random number generation. For example, random numbers shall not be predictable and shall have a sufficient entropy.

The TOE must ensure that no information about the produced random numbers is available to an attacker since they might be used for instance to generate cryptographic keys.

#### 4.2 Security Objectives for the Environment

#### 4.2.1 Objectives on Phase 1

O.DEV\_DIS

The smartcard IC designer must have procedures to control the sales, distribution, storage and usage of the software and hardware development tools and classified documents, suitable to maintain the integrity and the confidentiality of the assets of the TOE.

It must be ensured that:

- Tools are only delivered to the parties authorized personnel.

- Confidential information such as data sheets and general information on defined assets are only delivered to the parties authorized personnel on the basis of need-to-know.

O.SOFT DLV

The smartcard embedded software must be delivered from the smartcard embedded software developer (Phase 1) to the IC designer through a trusted delivery and verification procedure that shall be able to maintain the integrity of the software and its confidentiality, if applicable.

O.SOFT\_MECH

To achieve the level of security required by this Security Target Lite, the smartcard embedded software shall use IC security features and security mechanisms (for example, sensors) as specified in the smartcard IC documentation [TD].

O.DEV\_TOOLS

The smartcard embedded software shall be designed in a secure manner, by using exclusively software development tools (compilers, assemblers, linkers, simulators etc.) and software-hardware integration testing tools (emulators) that will grant the integrity of program and data.

#### 4.2.2 Objectives on Phase 2 (Development Phase)

O.SOFT\_ACS Embedded software shall be accessible only by authorized

personnel within the IC designer on the basis of

need-to-know.

O.DESIGN ACS IC specifications, detailed design, IC databases,

schematics/layout or any further design information shall be accessible only by authorized personnel within the IC designer on the basis of need-to-know (physical, personnel,

organizational, technical procedures).

O.DSOFT\_ACS Any IC dedicated software specification, detailed design,

source code or any further information shall be accessible only by authorized personnel within the IC designer on the

basis of need-to-know.

O.MASK\_FAB Physical, personnel, organizational, technical procedures

during photomask fabrication (including deliveries between photomasks manufacturer and IC manufacturer) shall ensure the integrity and confidentiality of the TOE.

O.MECH\_ACS Details of hardware security mechanisms shall be accessible

only by authorized personnel within the IC designer on the

basis of need-to-know.

O.TI\_ACS Security relevant technology information shall be accessible

only by authorized personnel within the IC designer on the

basis of need-to-know.

#### 4.2.3 Objectives on Phase 3 (Manufacturing Phase)

O.TOE PRT

The manufacturing process shall ensure that protection of the TOE from any kind of unauthorized use such as tampering or theft.

During the IC manufacturing and test operations, security procedures shall ensure the confidentiality and integrity of:

- TOE manufacturing data (to prevent any possible copy, modification, retention, theft or unauthorized use).

- TOE security relevant test programs, test data, databases and specific analysis methods and tools.

These procedures shall define a security system applicable during the manufacturing and test operations to maintain confidentiality and integrity of the TOE by control of:

- Packaging and storage.

- Traceability.

- Storage and protection of manufacturing process specific assets (such as manufacturing process documentation, further data, or samples)

- Access control and audit to tests, analysis tools, laboratories, and databases.

- Change/modification in the manufacturing equipment, management of rejects.

O.IC\_DLV

The delivery procedures from the IC manufacturer shall maintain the integrity and confidentiality of the TOE and its assets.

#### 4.2.4 Objectives on the TOE Delivery Process (Phases 4 to 7)

O.DLV\_PROTECT

Procedures shall ensure protection of TOE material and information under delivery, including the following objectives:

- Non-disclosure of any security relevant information.

- Identification of the elements under delivery.

- Meet confidentiality rules (confidentiality level, transmittal form, reception acknowledgement).

- Physical protection to prevent external damage.

- Secure storage and handling procedures are applicable for all TOEs (including rejected TOEs).

- Traceability of TOE during delivery including the following parameters:

- Origin and shipment details

- Reception, reception acknowledgement

- Location material and information

O.DLV AUDIT

Procedures shall ensure that corrective actions are taken in the event of improper operation in the delivery process (including, if applicable any non-conformance to the confidentiality convention) and highlight all non conformance to this process.

O.DLV RESP

Procedures shall ensure that people (shipping department, carrier, reception department) dealing with the procedure for delivery get the required skill, training and knowledge to meet the procedure requirements, and to act in full accordance with the above expectations.

#### 4.2.5 Objectives on Phase 4 to 6

O.TEST\_OPERATE

Appropriate functionality testing of the IC shall be used in phases 4 to 6.

During all manufacturing and test operations, security procedures shall be used through phases 4, 5, 6, to maintain confidentiality and integrity of the TOE and of its manufacturing and test data.

# 4.2.6 Objectives on Phase 7

O.USE\_DIAG Secure communication protocols and procedures shall be

used between smartcard and terminal.

O.USE\_SYS The integrity and the confidentiality of sensitive data stored

or handled by the system (terminals, communications....)

shall be maintained.

# **TOE Security Functional Requirements**

The TOE security functional requirements define the functional requirements for the TOE using only functional requirements components drawn from the Common Criteria part 2.

The minimum strength of function level for the TOE security requirements is SOF-high.

# 5.1 Functional Requirements Applicable to Phase 3 Only (Testing Phase)

# 5.1.1 User Authentication Before any Action (FIA\_UAU.2)

The TOE security functions shall require each user to be successfully authenticated before allowing any other TOE security functions-mediated actions on behalf of that user.

# 5.1.2 User Identification Before any Action (FIA\_UID.2)

The TOE security functions shall require each user to identify itself before allowing any other TOE security functions mediated actions on behalf of that user.

#### 5.1.3 User Attribute Definition (FIA\_ATD.1)

The TOE security functions shall maintain the following list of security attributes belonging to individual users:

Test mode access right

79

80

81

82

- Read, write fuses access rights

- Read AVR ROM access right

- Write AVR ROM access right

- Execute AVR ROM access right

- Read EEPROM access right

- Write EEPROM access right

- Execute EEPROM access right

- Read Crypto ROM access right

- Write Crypto ROM access right

- Execute Crypto ROM access right

- Read RAM access right

- Write RAM access right

- Execute RAM access right

- Read access right to peripherals and IO registers

- Write access right to peripherals and IO registers

- Execute access right to peripherals and IO registers

## 5.1.4 TOE Security Functions Testing (FPT\_TST.1)

The TOE security functions shall:

- Run a suite of self tests at the request of the authorized user to demonstrate the correct operation of the TOE security functions

- Provide authorized users with the capability to verify the integrity of TOE security functions data

- Provide authorized users with the capability to verify the integrity of stored TOE security functions executable code

# 5.1.5 Stored Data Integrity Monitoring (FDP\_SDI.1)

The TOE security functions shall monitor user data stored within the TOE scope of control for integrity errors on all objects, based on the following attributes:

- Test signatures from AVR ROM

- Test signatures and hardware test of RAM

- Test signatures from Crypto ROM

- Test signatures of EEPROM

84

# 5.2 Functional Requirements Applicable to Phases 3 to 7

# 5.2.1 Management of Security Functions Behaviour (FMT\_MOF.1)

The TOE security functions shall restrict the ability to:

- Enable the functions available in Test mode to the Test Mode Entry (TME) administrator

- Restrict the ability to disable the functions available in Test mode to the TME administrator

# 5.2.2 Management of Security Attributes (FMT\_MSA.1)

The TOE security functions shall enforce the ACSF\_Policy (Access Control Security Functions Policy) and IFCSF\_Policy (Information Flow Control Security Functions Policy) to restrict the ability to access the security attributes to TME administrator and Firewall supervisor/non-supervisor modes.

85

86

88

The ACSF\_Policy is not described in this document. See Table 5-1 for further information on the IFCSF\_Policy.

#### 5.2.3 Security Roles (FMT SMR.1)

The TOE security functions shall:

- Maintain the role of TME administrator

- Maintain the role of Firewall supervisor/non-supervisor modes

- Be able to associate users with roles

#### 5.2.4 Static Attribute Initialization (FMT\_MSA.3)

The TOE security functions shall:

- Enforce the ACSF\_Policy and IFCSF\_Policy to provide restrictive default values for security attributes that are used to enforce the security functions policy

- Allow the TME administrator to specify alternate initial values to override the default values when an object or information is created

90

91

#### 5.2.5 Complete Access Control (FDP\_ACC.2)

The TOE security functions shall enforce the ACSF\_Policy on:

- TME administrator, Firewall supervisor/non-supervisor modes.

- AVR ROM, EEPROM, RAM, Crypto ROM, peripheral and IO registers.

- And all operations among subjects and objects covered by the security functions policy.

The TOE security functions shall ensure that all operations between any subject in the TOE scope of control and any object within the TOE scope of control are covered by an access control security functions policy.

#### 5.2.6 Security Attribute Based Access Control (FDP\_ACF.1)

The TOE security functions shall enforce the ACSF\_Policy to objects based on:

- Read AVR ROM access right

- Write AVR ROM access right

- Execute AVR ROM access right

- Read EEPROM access right

- Write EEPROM access right

- Execute EEPROM access right

- Read Crypto ROM access right

- Write Crypto ROM access right

- Execute Crypto ROM access right

- Read RAM access right

- Write RAM access right

- Execute RAM access right

- Read peripheral and IO registers access right

- Write peripheral and IO registers access right

- Execute peripheral and IO registers access right

The TOE security functions shall enforce the following rules to determine if an operation among controlled subjects and controlled objects is allowed.

#### Firewall rules, that are not disclosed in this ST-Lite document.

The TOE security functions shall explicitly authorize access of subjects to objects based on the following additional rules: **no additional rules**.

92

# 5.2.7 Subset Information Flow Control (FDP\_IFC.1)

The TOE security functions shall enforce the IFCSF\_Policy on TME administrator, test commands and test operations that cause controlled information to flow between the:

- AVR ROM and the TME administrator

- EEPROM and the TME administrator

- Crypto ROM and the TME administrator

- RAM and the TME administrator

- Peripheral and IO registers and the TME administrator

# 5.2.8 Simple Security Attributes (FDP\_IFF.1)

The TOE security functions shall enforce the IFCSF\_Policy based on the following types of subject and information security attributes: **test command syntax**.

95 The TOE security functions shall:

93

94

96

97

- Permit an information flow between a controlled subject and controlled information via a controlled operation if the following rules hold: test command syntax rules.

- Provide no additional information flow control security functions policy rules.

- Enforce no additional security functions policy capabilities.

The TOE security functions shall explicitly authorize an information flow based on the following rules:

Test command syntax rules, based on test command syntax, that explicitly **authorize** information flows between TME administrator and:

- AVR ROM

- EEPROM

- Crypto ROM

- RAM

- Peripheral and IO registers

The TOE security functions shall explicitly deny an information flow based on the following rules:

Test command syntax rules, based on test command syntax, that explicitly **deny** information flows between TME administrator and:

- AVR ROM

- EEPROM

- Crypto ROM

- RAM

- Peripheral and IO registers

100

101

#### **IFCSF-Policy**

Table 5-1 IFCSF-Policy

Rules Test command syntax rules

Attribute Test command syntax

TME Administrator Data flow (1)

(1) All information about possible data flow and Test command syntax can be found in [STI], [TMR-USER], [TestROMUG], [TestROMDD] and [TMRE2].

#### 5.2.9 Potential Violation Analysis (FAU\_SAA.1)

The TOE Security Functions shall be able to apply a set of rules in monitoring the audited events and based upon these rules indicate a potential violation of the TOE Security Policy.

The TOE security functions shall enforce the following rules for monitoring audited events:

- a) Accumulation or combination of abnormal environmental conditions (Supply voltage, clock input frequency, temperature, UV light) known to indicate a potential security violation.

- b) Accumulation or combination of physical tampering (Micro-probing, critical FIB modification) known to indicate a potential security violation.

- c) Accumulation or combination of Firewall violations (user trying to illegally access controlled memories or objects, user trying to execute illegal opcodes) known to indicate a potential security violation.

- d) Accumulation of watchdog violations known to indicate a potential security violation.

- e) No other rules.

#### 5.2.10 Unobservability (FPR\_UNO.1)

The TOE security functions shall ensure that any users are unable to observe the operation of TOE internal activity on TOE objects by authorized users or subjects.

#### 5.2.11 Notification of Physical Attack (FPT\_PHP.2)

The TOE security functions shall provide:

104

105

106

107

- Unambiguous detection of physical tampering that might compromise the TOE security functions.

- The capability to determine whether physical tampering with the TOE security functions's devices or TOE security functions's elements has occurred.

For values of voltage, clock input frequency, temperature and UV light which go outside acceptable bounds, for micro-probing and critical FIB modification, for Firewall rules violations (including illegal opcodes), and for watchdog violations, the TOE security functions shall monitor the devices and elements and notify the Firewall-supervisor when physical tampering with the TOE security functions' devices or TOE security functions' elements has occurred.

#### 5.2.12 Resistance to Physical Attack (FPT PHP.3)

The TOE security functions shall resist tampering of voltage, clock input frequency, temperature, UV light, micro-probing, critical FIB modification, Firewall rules violations (including illegal opcodes), and watchdog violations to the TOE and its security functions by responding automatically such that the TOE security policy is not violated.

#### 5.2.13 Cryptographic Operation (FCS\_COP.1)

The TSF shall perform hardware data encryption and decryption in accordance with the:

- DES cryptographic algorithm using 56-bit cryptographic key sizes that meets the Data Encryption Standard (DES), FIPS PUB 46-3, 25th October, 1999.

- Triple Data Encryption Standard (TDES) cryptographic algorithm using 112-bit cryptographic key sizes that meets the E-D-E two-key triple-encryption implementation of the Data Encryption Standard, FIPS PUB 46-3, 25th October, 1999.

- Hardware data hash and signature in accordance with the SHA-1 cryptographic algorithm using no cryptographic key that meets the Secure Hash Standard, FIPS PUB 180-1, 17th April, 1995.

The TSF shall perform hardware data encryption and decryption in accordance with the:

- RSA without CRT cryptographic algorithm using 512-bit, 1024-bit, 2048-bit cryptographic key sizes that meets no standard.

- RSA with CRT cryptographic algorithm using 512-bit, 1024-bit, 2048-bit cryptographic key sizes that meets no standard

109

110

111

112

#### 5.2.14 Cryptographic Key Generation (FCS\_CKM.1)

The TSF shall generate cryptographic keys in accordance with cryptographic key generation algorithm Miller-Rabin algorithm with confidence criteria (t) between 0 and 255 and specified cryptographic key sizes 512-bit, 1024-bit, 2048-bit (respectively 2 primes of 256 bits, 512 bits and 1024 bits) that meet the NIST special publication 800-2, April 1991.

# 5.3 TOE Security Assurance Requirements

The assurance requirement is EAL4 augmented of additional assurance components listed in the following sections.

Some of these components are hierarchical ones to the components specified in EAL4.

All the components are drawn from Common Criteria Part 3, V2.1.

#### 5.3.1 ADV\_IMP.2 Implementation of the TSF

#### **Developer actions elements**

The developer shall provide the implementation representation for the entire TOE security functions.

# Content and presentation of evidence elements

The implementation representation shall:

- Unambiguously define the TOE security functions to a level of detail such that the TOE security functions can be generated without further design decisions

- Be internally consistent

- Describe the relationships between all portions of the implementation

#### **Evaluator actions elements**

114 The evaluator shall:

- Confirm that the information provided meets all requirements for content and presentation of evidence.

- Determine that the implementation representation is an accurate and complete instantiation of the TOE security functional requirements.

#### 5.3.2 ALC\_DVS.2 Sufficiency of Security Measures

#### **Developer actions elements**

The developer shall produce development security documentation.

# Content and presentation of evidence elements

The development security documentation shall:

- Describe all the physical, procedural, personnel, and other security measures that are necessary to protect the confidentiality and integrity of the TOE design and implementation in its development environment.

- Provide evidence that these security measures are followed during the development and maintenance of the TOE.

The evidence shall justify that the security measures provide the necessary level of protection to maintain the confidentiality and integrity of the TOE.

#### **Evaluator actions elements**

The evaluator shall confirm that the:

- Information provided meets all requirements for content and presentation of evidence

- Security measures are being applied

#### 5.3.3 AVA\_VLA.4 Highly Resistant

#### **Developer actions elements**

The developer shall:

- Perform and document an analysis of the TOE deliverables searching for ways in which a user can violate the TOE security policy

- Document the disposition of identified vulnerabilities

# Content and presentation of evidence elements

120 The documentation shall:

- Show, for all identified vulnerabilities, that the vulnerability cannot be exploited in the intended environment for the TOE.

- Justify that the TOE, with the identified vulnerabilities, is resistant to obvious penetration attacks.

- The evidence shall show that the search for vulnerabilities is systematic.

#### AT90SC9608RC Security Target Lite

The analysis documentation shall provide a justification that the analysis completely addresses the TOE deliverables.

#### **Evaluator actions elements**

#### 123 The evaluator shall:

- Confirm that the information provided meets all requirements for content and presentation of evidence

- Conduct penetration testing, building on the developer vulnerability analysis, to ensure the identified vulnerabilities have been addressed.

- Perform independent vulnerability analysis

- Perform independent penetration testing, based on the independent vulnerability analysis, to determine the exploitability of additional identified vulnerabilities in the intended environment.

- Determine that the TOE is resistant to penetration attacks performed by an attacker possessing a high attack potential.

# **TOE Summary Specification**

This section defines the TOE security functions, and Figure 6-1 on page 54 specifies how they satisfy the TOE security functional requirements.

# 6.1 TOE Security Functions

# 6.1.1 Test Mode Entry (SF1)

- SF1 shall ensure that only authorized users shall be permitted to enter Test mode. This is provided by TME conditions that are required to enable the TOE to enter Test mode.

- All test entry requirements occur while the TOE is held in reset and failure in any one will prevent TME. It is required that the TOE satisfies the test entry conditions during any internal reset condition.

- It is not possible to move from User mode to Test mode. Any attempt to do this, for example, by forcing internal nodes will be detected and the security functions will disable the ability to enter Test mode.

- The Strength of Function claimed for the TME security function is high.

#### 6.1.2 Protected Test Memory Access (SF2)

- SF2 shall ensure that, although authenticated users can have access to memories using commands in Test mode, they cannot access directly their contents.

- Only authorized design and production engineers running test on the TOE will have access to the TME conditions.

- The Strength of Function claimed for the Protected Test Memory Access security function is high.

#### 6.1.3 Test Mode Disable (SF3)

SF3 shall make provision for Test Mode Disable master fuses which, once blown, shall ensure that none of the test features are available, not even to authenticated users in Test mode.

134

135

137

#### 6.1.4 TOE Testing (SF4)

SF4 shall provide embedded hardware test circuitry with high fault coverage to prevent faulty devices being released in the field. Devices with manufacturing problems (short circuits, open nets, ...) could lead to a poor level of security by disabling some security functions.

Testing of Security Functions is dependent on a fault free and fully functional TOE. The RAM, ROM and standard cell logic (including the MCU) is tested by functional tests under the control of the test interface circuit. EEPROM is tested through the test interface circuit by external stimulus. CPU to EEPROM data flow will also be tested by functional tests, run from the EEPROM, using test software loaded under the control of the test interface circuit.

To conform with ISO 7816 standards the TOE embedded software will always return an Anwer-To-Reset command via the serial I/O port. This contains messages with information on the integrity and identification of the device. An ATR also verifies significant portions of device hardware (CPU, ROM, EEPROM and logic).

# 6.1.5 Data Error Detection (SF5)

SF5 shall provide means for performing data error detection.

Means of performing checksum error detection and parity error detection is provided. The 32-bit Checksum Accelerator or the CRC-16 hardware peripheral can be used by the embedded software to compute fast data error detection on the program and/or data memories before starting any operation.

#### 6.1.6 FireWall (SF6)

SF6 shall enforce access control based on the FireWall rules as defined in the ACSF Policy:

#### **Memory protection**

138

139

- The FireWall defines different modes to execute embedded software (supervisor / non-supervisor).

- The different modes provide restricted access privilege to the memories, and to the MCU peripheral registers. In case of illegal accesses performed by the embedded software, a security action is invoked.

#### **Illegal Address**

If an illegal address is accessed, then a security action is invoked.

#### **Illegal Opcode**

If an attempt is made to execute any opcode that is not implemented in the instruction set, a security action is invoked.

# 6.1.7 Event Audit (SF7)

The TOE shall provide an Event Audit security function (SF7) to enforce the following rules for monitoring audited events:

Accumulation or combination of the following auditable events would indicate a potential security violation:

- 1. The external voltage supply goes outside acceptable bounds.

- 2. The external clock signal goes outside acceptable bounds.

- 3. The ambient temperature goes outside acceptable bounds.

- 4. Application program abnormal runaway.

- 5. Attempts to physically probe the device.

- 6. Attempts to gain illegal access to reserved RAM memory locations.

- 7. Attempts to gain illegal access to reserved EEPROM memory locations.

- 8. Attempts to gain illegal access to reserved peripheral or IO register locations.

- 9. Attempts to execute instruction to read the program memory from the non-supervisor program location.

- 10. Attempts to move the RAM stack to an illegal RAM memory location.

- 11. Attempts to execute an AVR opcode that is not implemented.

- 12. Attempts to illegally write access the device's EEPROM.

- 13. Attempts to gain illegal access to supervisor modes.

- 14. The exposition to UV light goes outside acceptable bounds.

These events are audited by IO register bits or other hardware mechanisms accessible to the embedded software.

The Strength of Function claimed for the Event audit security function is high.

### 6.1.8 Event Action (SF8)

SF8 shall provide an Event Action security function to register occurrences of audited events and take appropriate action. Detection of such occurrences will cause an information flag to be set, and may cause one of the following to occur if the violation warrants such action:

- Memory wiping actions

- Different levels of immediate resets

- Different levels of security interrupts

- Event Action depends on the type of Event (see [TD] for more information).

#### 6.1.9 Unobservability (SF9)

143

- SF9 shall ensure that users/third parties will have difficulty observing the following operations on the TOE by the described means.

- 1. Extracting information, relating to any specific resource or service being used, by monitoring power consumption

- 2. Extracting information, relating to any specific resource or service being used, carrying out timing analyses on cryptographic functions

- 3. Extracting information, relating to any specific resource or service being used, by using mechanical, electrical or optical means, in order to examine the topology of the TOE, including address and data buses and regular structures.

- The Strength of Function claimed for the Unobservability security function is high.

#### 6.1.10 Cryptography (SF10)

- The TSF shall provide a cryptographic algorithm to be able to transmit and receive objects in a manner protected from data retrieval or modification.

- The TSF shall provide hardware DES, TDES data encryption/decryption capability, and SHA-1 data signing capability. The TSF shall also provide hardware RSA without CRT (i.e. modular exponentiation) data encryption/decryption capability, as well as RSA with CRT data encryption/decryption capability [TBX].

- Those may be used by the smartcard embedded software to support data encryption and decryption for maintaining data integrity, and protect against sensitive data unauthorized disclosure.

- The TSF shall provide a RNG to support security operations performed by cryptographic applications. This RNG shall not be predictable, have sufficient entropy, and not leaking information related to the value of the generated random numbers as this leakage could be used to retrieve cryptographic keys for instance.

- The TSF shall provide RSA cryptographic key generation capability using Miller Rabin algorithm with confidence criteria (t parameter) between 0 and 255.

- An assessment of the strength of the:

- DES algorithm does not form part of the evaluation

- TDES algorithm does not form part of the evaluation

- SHA-1 algorithm does not form part of the evaluation

- RSA without CRT algorithm does not form part of the evaluation

- RSA with CRT algorithm does not form part of the evaluation

- Miller Rabin algorithm does not form part of the evaluation

- The TSF shall also provide cryptographic primitives to ease the customer proprietary software implementation of these algorithms (multiply, square, ...) as well as DSA and EC-DSA data signature in the AVR embedded software.

#### 6.1.11 Security Functions Based on Permutations/Combinations

- The description of the security functions using permutations and/or combination properties is not disclosed in this document.

- Further details on these mechanisms and on the Strength of Function Analysis performed by ATMEL can be found in [SOF].

Table 6-1 Relationship Between Security Requirements and Security Functions

|                         |     | Security Functions |                              |                   |             |                      |          |             |              |                 |              |

|-------------------------|-----|--------------------|------------------------------|-------------------|-------------|----------------------|----------|-------------|--------------|-----------------|--------------|